Can message center 15 mask register 0 (cnm15m0), Can message center 15 mask register 1 (cnm15m1), Can 0 message center 15 mask register 2 (cnm15m2) – Maxim Integrated High-Speed Microcontroller Users Guide: DS80C390 Supplement User Manual

Page 129: Can 0 message center 15 mask register 3 (cnm15m3)

High-Speed Microcontroller User’s Guide: DS80C390 Supplement

129 of 158

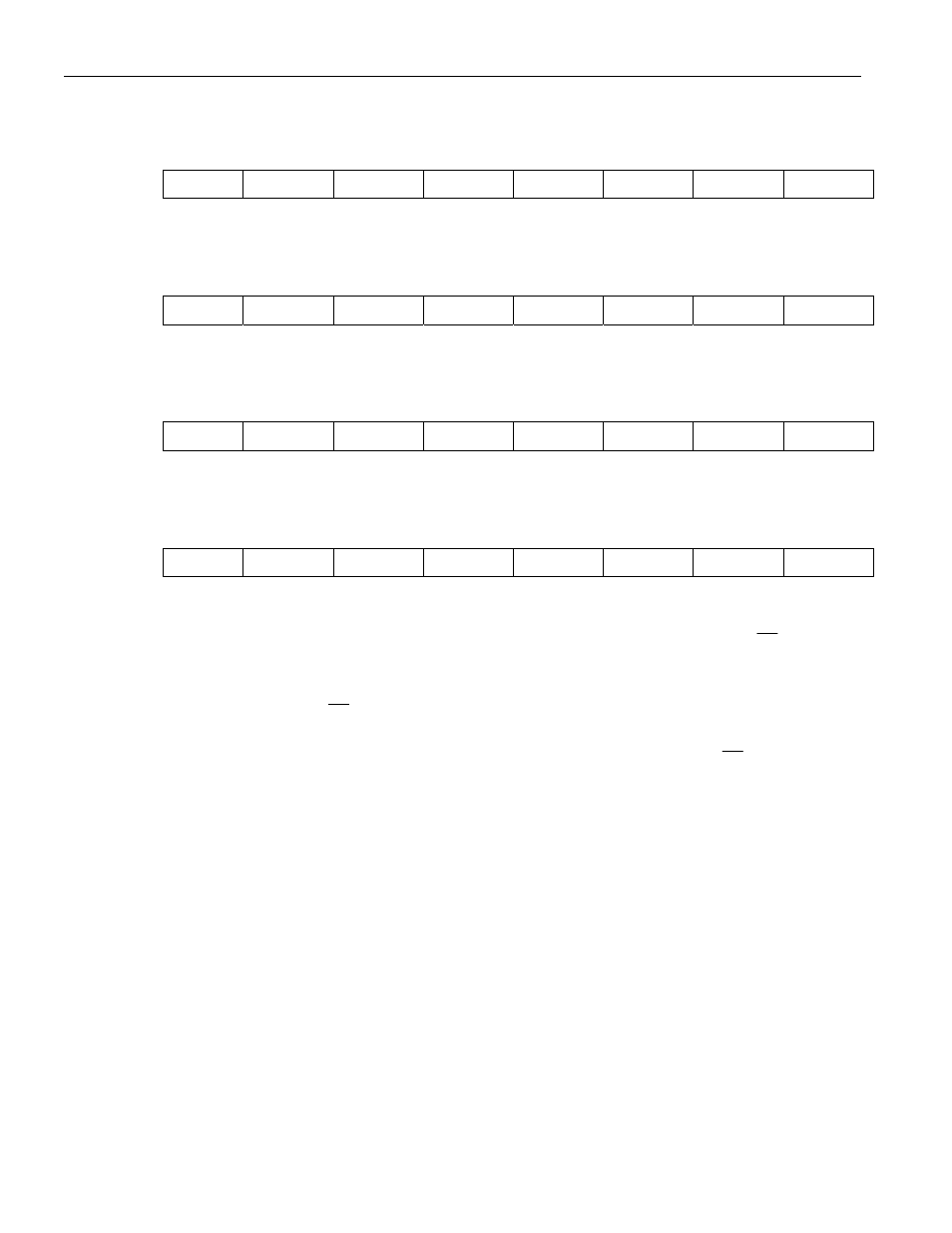

CAN Message Center 15 Mask Register 0 (CnM15M0)

MOVX

Address

1

7

6

5

4

3

2

1

0

xxxx0Ch MASK28 MASK27 MASK26 MASK25 MASK24 MASK23 MASK22 MASK21

CAN Message Center 15 Mask Register 1 (CnM15M1)

MOVX

Address

1

7

6

5

4

3

2

1

0

xxxx0Dh MASK20 MASK19 MASK18 MASK17 MASK16 MASK15 MASK14 MASK13

CAN 0 Message Center 15 Mask Register 2 (CnM15M2)

MOVX

Address

1

7

6

5

4

3

2

1

0

xxxx0Eh MASK12 MASK11 MASK10

MASK9 MASK8 MASK7 MASK6 MASK5

CAN 0 Message Center 15 Mask Register 3 (CnM15M3)

MOVX

Address

1

7

6

5

4

3

2

1

0

xxxx0Fh MASK4 MASK3 MASK2 MASK1 MASK0

0

0

0

MASK28-MASK0 CAN Message Center 15 Mask Registers 0-3. These registers function as the

mask when performing the Extended Global Identification test (EX/ST =1) for

Message Center 15 only. These registers can only be modified during a software

initialization (SWINT=1).

When EX/ST =1, the 29 bits of the message ID will be compared against the 29

bits of the CAN Message Center 15 Arbitration Registers, using the 29 bits of the

CAN Message Center 15 Mask Registers as a mask. When EX/ST =0, the 11 bits

of the message ID will be compared against the most significant 11 bits of the

CAN Message Center 15 Arbitration Registers, using the most significant 11 bits

of the CAN Message Center 15 Mask Registers as a mask. Any bit in the CAN

Message Center 15 Mask Registers set to 0 will ignore the state of the

corresponding bit in the incoming message ID field when performing the test.

Any bit in the CAN Message Center 15 Mask Registers set to 1 will force the

state of the corresponding bit in the incoming message ID field and CAN message

center arbitration Registers 0-3 to match before considering the incoming message

a match.

The three least significant bits in the CnM15M3 register are not used, and will not

perform any comparison of these bit locations. A read of these bits will always

return 0, and writes to these bits will be ignored.

Programming all Mask registers to 00h effectively disables the Message Center 15

ID test, accepting all messages. As such the Message Center 15 mask registers act

as a don’t care following a system Reset.