Port 4 (p4), 4 (p4) – Maxim Integrated High-Speed Microcontroller Users Guide: DS80C390 Supplement User Manual

Page 14

High-Speed Microcontroller User’s Guide: DS80C390 Supplement

14 of 158

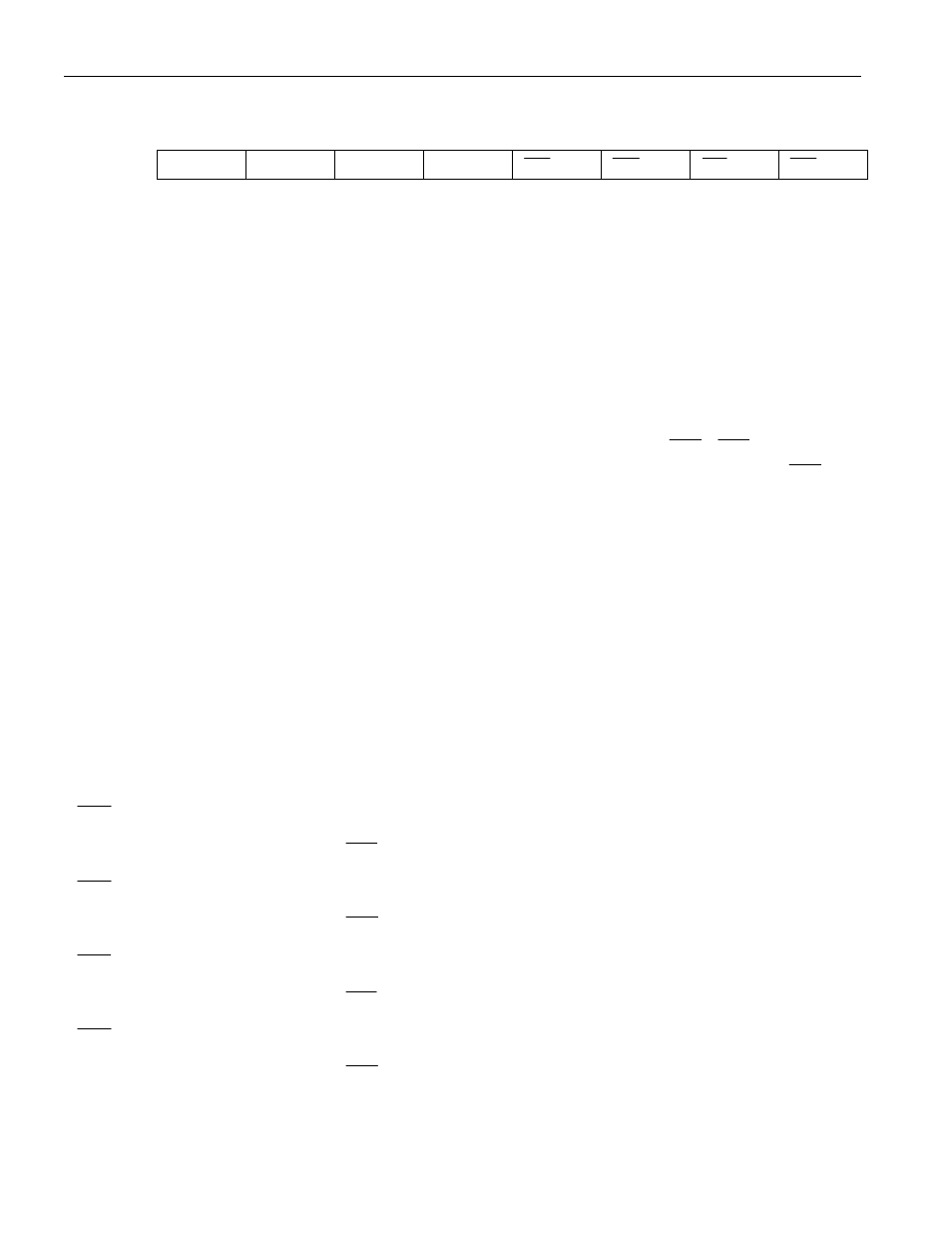

PORT 4 (P4)

7 6 5 4 3 2 1 0

SFR 80h

A19/P4.7 A18/P4.6 A17/P4.5 A18/P4.4

3

CE

/P4.3

2

CE

/P4.2

1

CE

/P4.1

0

CE

/P4.0

RW-0 RW-0 RW-0 RW-0 RW-1 RW-1 RW-1 RW-1

R = Unrestricted Read, W = Unrestricted Write, -n = Value after Reset

P4.7–P4.0

Port 4. This port functions as a general-purpose I/O port. In addition, all the pins

have an alternative function associated with the memory interface described

below. The selection of general I/O or memory interface function for the Port 4

pins is controlled by the P4CNT(92h) register. Port pins configured as I/O will

reflect the state of the corresponding port pin. Port pins assigned to memory

interface functions will appear as 1 when read. The associated SFR bit must be

programmed to logic one before the pin can be used in its alternate function

capacity. The reset state of this register and the P4CNT register will configure the

device to so that A19–A16 function as address lines and

3

CE

0

CE

−

are active.

The first opcode fetch following a reset will therefore be at 00000h with

0

CE

asserted.

A19

Bit 7

Program/Data Memory Address 19.

When this bit is set to a logic one and the

P4CNT register is configured correctly, the corresponding device pin will

represent the A19 memory signal.

A18

Bit 6

Program/Data Memory Address 18.

When this bit is set to a logic one and the

P4CNT register is configured correctly, the corresponding device pin will

represent the A18 memory signal.

A17

Bit 5

Program/Data Memory Address 17.

When this bit is set to a logic one and the

P4CNT register is configured correctly, the corresponding device pin will

represent the A17 memory signal.

A16

Bit 4

Program/Data Memory Address 16.

When this bit is set to a logic one and the

P4CNT register is configured correctly, the corresponding device pin will

represent the A16 memory signal.

CE3

Bit 3

Program Memory Chip Enable 3.

When this bit is set to a logic one and the

P4CNT register is configured correctly, the corresponding device pin will

represent the CE3 memory signal.

CE2

Bit 2

Program Memory Chip Enable 2.

When this bit is set to a logic one and the

P4CNT register is configured correctly, the corresponding device pin will

represent the CE2 memory signal.

CE1

Bit 1

Program Memory Chip Enable 1.

When this bit is set to a logic one and the

P4CNT register is configured correctly, the corresponding device pin will

represent the CE1 memory signal.

CE0

Bit 0

Program Memory Chip Enable 0.

When this bit is set to a logic one and the

P4CNT register is configured correctly, the corresponding device pin will

represent the CE0 memory signal.