Extended stack pointer register (esp), Xtended, Tack – Maxim Integrated High-Speed Microcontroller Users Guide: DS80C390 Supplement User Manual

Page 30: Ointer, Egister, Esp), Ddress

High-Speed Microcontroller User’s Guide: DS80C390 Supplement

30 of 158

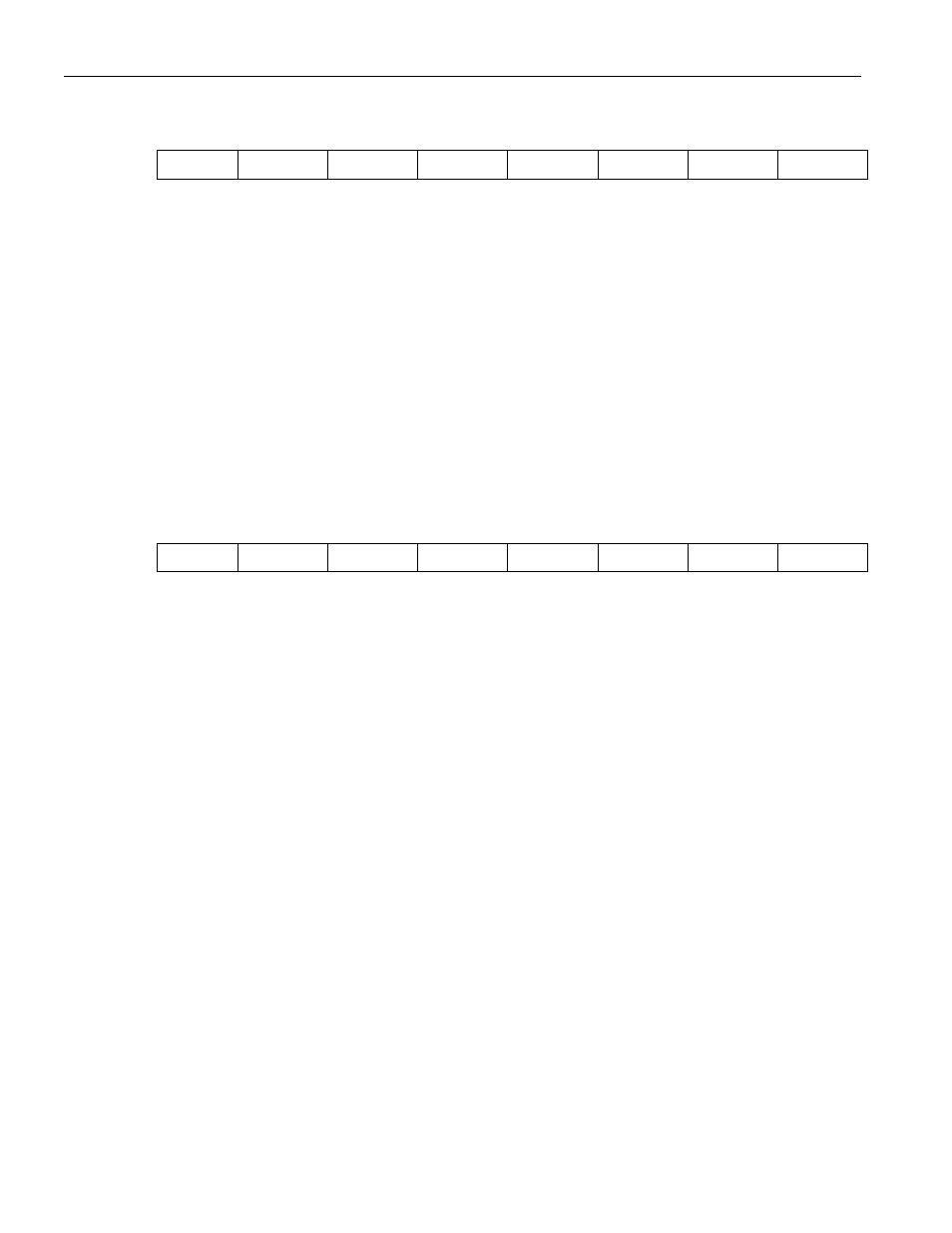

EXTENDED STACK POINTER REGISTER (ESP)

7 6 5 4 3 2 1 0

SFR

9Bh

1 1 1 1 1 1

ESP.1

ESP.0

R-1 R-1 R-1 R-1 R-1 R-1 RW-0

RW-0

R = Unrestricted Read, W = Unrestricted Write, -n = Value after Reset

Bits 7-2

Reserved

ESP.1-0

Bits 1-0

Extended Stack Pointer. This register contains the upper 2 bits of the 10-bit

stack pointer. When the SA bit is set, any overflow of the SP from FFh to 00h

will increment the ESP by 1, and any underflow of the SP from 00h to FFh will

decrement the ESP by 1. The ESP register is ignored when SA = 0, but is still

read/write accessible. Configuring the 4K block of SRAM as program and/or data

memory (IDM1,IDM0=11b) will disable the extended stack mode. Internal logic

will take into consideration the programming conditions imposed by the SA,

IDM1 and IDM0 bits within the MCON register, to allow access to the 1K Stack

Memory. See ACON register for more detail.

ADDRESS PAGE REGISTER (AP)

7 6 5 4 3 2 1 0

SFR 9Ch

RW-0 RW-0 RW-0 RW-0 RW-0 RW-0 RW-0 RW-0

R = Unrestricted Read, W = Unrestricted Write, -n = Value after Reset

AP.7-0

Bits 7-0

Address Page Register. The AP Register (AP) supports extended program and

data addressing (>64KB) capabilities in the 22-bit paged addressing mode (AM1,

AM0 = 01b), and is fully compatible with the original 8052 16-bit addressing

mode. When executing LJMP or LCALL instructions in paged addressing mode,

the microcontroller automatically loads bits 23:16 of the program counter with

the contents of the AP register to calculate the new LCALL or LJMP address.

The AP register affects only the previous instructions, and is not incremented

during a program counter rollover from FFFFh to 0000h. This register is a

general-purpose SFR when not operating in 22-bit paged mode.

Executing interrupts while in 22-bit paged addressing mode pushes the three

bytes of the program counter onto the stack, but not the AP register itself. The AP

register should be saved at the beginning of the ISR if it will be modified inside

the ISR. Following the execution of a RETI instruction, the processor will

automatically reload the entire 24 value of the PC with the original address from

the stack, again leaving the contents of the AP register unchanged.