Power management register (pmr), Ower, Anagement – Maxim Integrated High-Speed Microcontroller Users Guide: DS80C390 Supplement User Manual

Page 57: Egister, Pmr)

High-Speed Microcontroller User’s Guide: DS80C390 Supplement

57 of 158

POWER MANAGEMENT REGISTER (PMR)

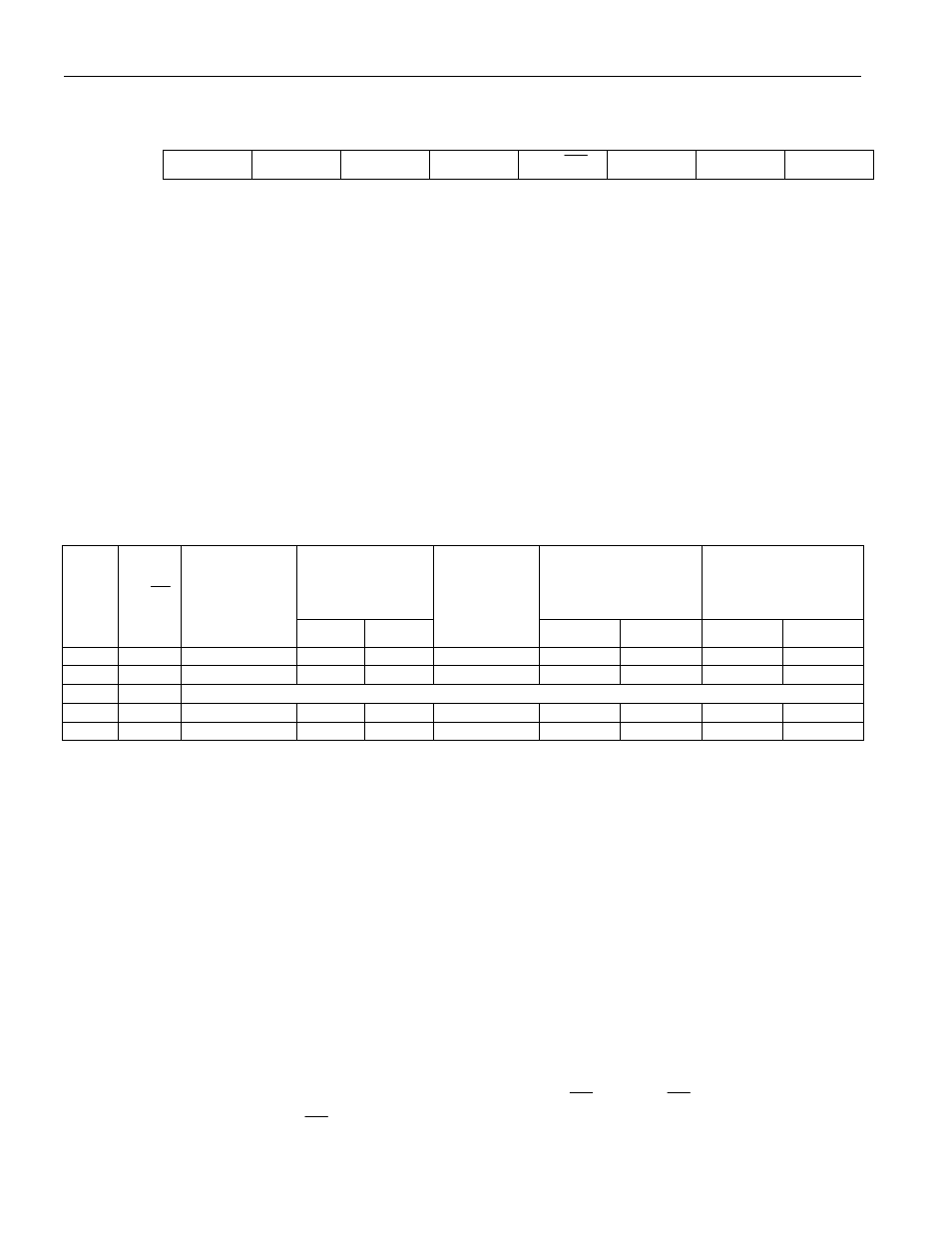

7 6 5 4 3 2 1 0

SFR C4h

CD1

CD0

SWB

CTM

4X/ X

2 ALEOFF 1

1

R*-1 R*-0 RW-0 R*-0 R*-0 RW-0 R-1 R-1

R = Unrestricted Read, W = Unrestricted Write, * = See description below, -n = Value after Reset

CD1, CD0

Bits 7-6

Clock Divide Control 1-0. These bits select the number of crystal oscillator

clocks required to generate one machine cycle. Switching between modes

requires a transition through the divide-by-4 mode (CD1, CD0=10b). For

example, to go from 1 to 1024 clocks per machine cycle the device must first go

from 1 to 4 clocks per cycle, and then from 4 to 1024 clocks per cycle. Attempts

to perform an invalid transition will be ignored. The setting of these bits affects

the timers and serial ports as shown below. Attempts to change these bits to the

frequency multiplier (1 or 2 clocks per cycle) setting will fail when running from

the internal ring oscillator. In addition, it is not possible to change these bits to

the 1024 clocks per machine cycle setting while the switchback enable bit (SWB)

is set and any of the switchback sources (external interrupts or serial port transmit

or receive activity) are active.

OSC CYCLES

PER TIMER 0/1/2

CLOCK.

OSC CYCLES PER

SERIAL PORT CLK,

MODE 0

OSC CYCLES PER

SERIAL PORT CLK,

MODE 2

CD1:0 4X/ 2X

OSCILLATOR

CYCLES PER

MACHINE.

CYCLE

TxM=0 TxM=1

OSC CYCLES

PER TIMER 2

CLK, BAUD

RATE GEN.

SM2=0 SM2=1 SMOD=0

SMOD=1

00 1

1

12 1

2

3

1

64

32

00 0

2

12 2

2

6

2

64

32

01 x

Reserved

10 x

4

12 4

2

12

4

64

32

11 x

1024 3072

1024 512

3072 1024 64

32

SWB

Bit 5

Switchback Enable. This bit allows an enabled external interrupt or serial port

activity to force the Clock Divide Control bits to the divide-by-4 state (10) when

the microcontroller is in the divide-by-1024 state. Upon internal

acknowledgement of an external interrupt, the device will switch modes at the

start of the jump to the interrupt service routine. Note that this means that an

external interrupt must actually be recognized (i.e., be enabled and not masked by

higher priority interrupts) for the switchback to occur. For serial port reception,

the switch occurs at the start of the instructions following the falling edge of the

start bit.

CTM

Bit 4

Crystal Multiplier Enable. The CTM bit enables/disables the Crystal Clock

Multiplier. The CTM bit can be changed only when the CD1 and CD0 bits are set

to divide-by-4 mode and the RGMD is cleared to 0. When cleared this bit

disables the Crystal Clock Multiplier to save energy. Setting this bit enables the

Crystal Clock Multiplier, permitting the use of the 1 or 2 clock per machine cycle

speeds. The following procedure must be performed when setting the CTM bit.

1. Select the desired clock rate by the 4X/ X

2 bit. (4X/ X

2 =1, 1 clock per cycle,

4X/ X

2 =0, 2 clocks per cycle).