Bit contiguous addressing mode – Maxim Integrated High-Speed Microcontroller Users Guide: DS80C390 Supplement User Manual

Page 116

High-Speed Microcontroller User’s Guide: DS80C390 Supplement

116 of 158

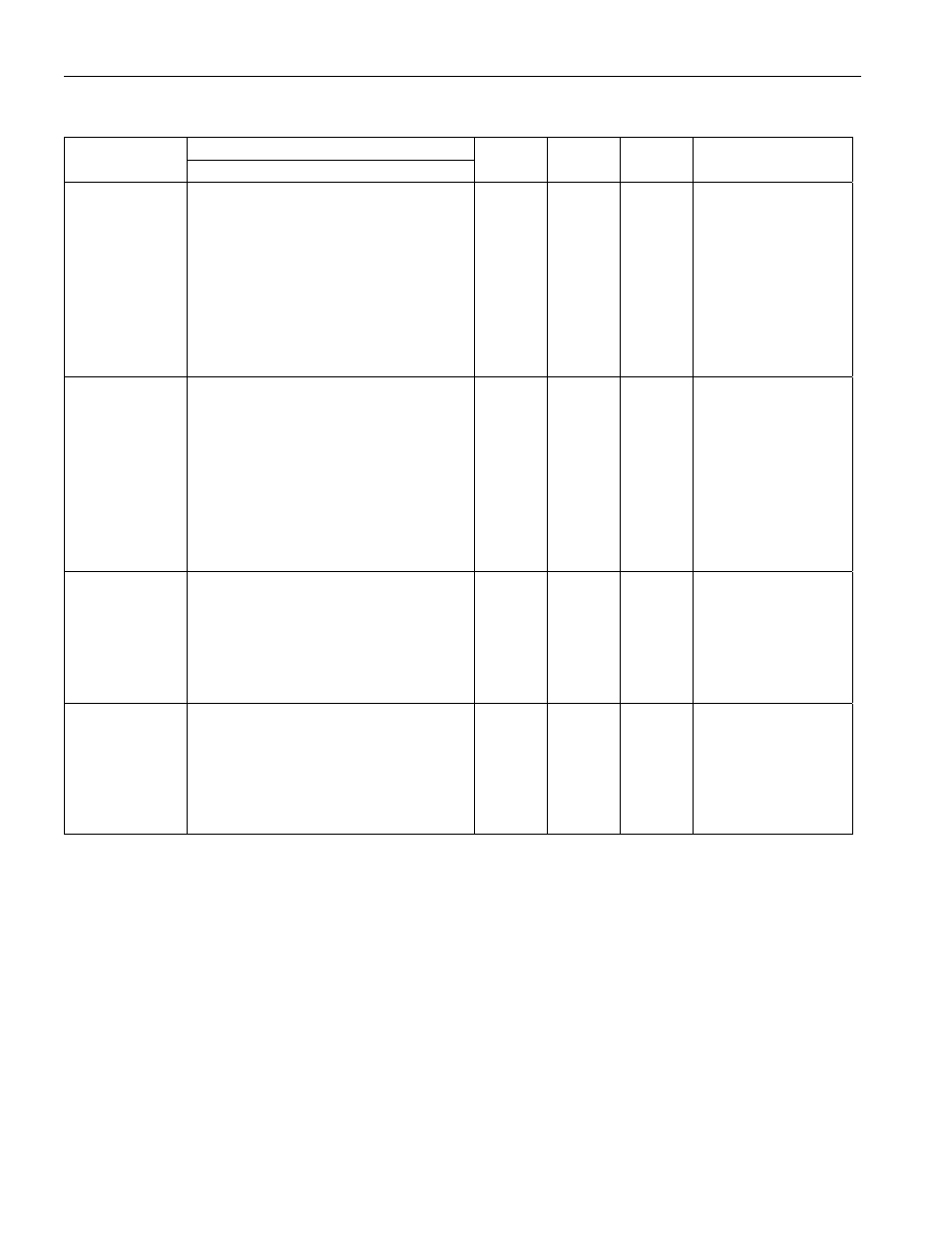

The modification of the instructions in the 22-bit page address mode is summarized in the following

table.

INSTRUCTION CODE

MNEMONIC D

7

D

6

D

5

D

4

D

3

D

2

D

1

D

0

HEX

BYTE

CYCLE

EXPLANATION

ACALL addr

11

a

10

a

7

a

9

a

6

a

8

a

5

1

a

4

0

a

3

0

a

2

0

a

1

1

a

0

Byte 1

Byte 2

2 4

(PC

15:0

)=(PC

15:0

)+2

(SP) = (SP) + 1

((SP)) = (PC

7:0

)

(SP) = (SP) + 1

((SP)) = (PC

15-8

)

(SP) = (SP) + 1

((SP))=(PC

23:16

)

(PC

10:0

)=addr11

(PC

23:16

)=(AP

7:0

)

LCALL addr

16

0

a

15

a

7

0

a

14

a

6

0

a

13

a

5

1

a

12

a

4

0

a

11

a

3

0

a

10

a

2

1

a

9

a

1

0

a

8

a

0

12

Byte 2

Byte 3

3 5

(PC

15:0

)=(PC

15:0

)+3

(SP) = (SP) + 1

((SP)) = (PC

7:0

)

(SP) = (SP) + 1

((SP)) = (PC

15-8

)

(SP) = (SP) + 1

((SP))=(PC

23:16

)

(PC)=addr16

(PC

23:16

)=(AP

7:0

)

RET

0 0 1 0 0 0 1 0 22

1

5 (PC

23:16

)=((SP))

(SP)=(SP)-1

(PC

15-8

)=((SP))

(SP)=(SP)-1

(PC

7:0

)=((SP))

(SP)=(SP)-1

RETI

0 0 1 1 0 0 1 0 32

1

5 (PC

23:16

)=((SP))

(SP)=(SP)-1

(PC

15-8

)=((SP))

(SP)=(SP)-1

(PC

7-0

)=((SP))

(SP)=(SP)-1

22-BIT CONTIGUOUS ADDRESSING MODE

When the AM1 bit is set, the DS80C390 will operate in its 22-bit contiguous addressing mode. This

addressing mode is supported by a full 22-bit Program Counter with eight modified instructions that

operate over the full 22-bit address range. All modified branching instructions will automatically store

and restore the entire contents of the 22-bit Program Counter. The 22-bit DPTR and DPTR1 registers will

function identically to the Program Counter to allow access to the full 22- bit data memory range.

All the DS80C390 instruction opcodes retain binary compatibility to the 8051. Modified instructions are

only different with respect to their cycle/byte/operand count and operate within a contiguous 24-bit

address field. Note that all instructions which utilize the DPTR register now make use of a full 24-bit

register (DPTR=DPX+DPH+DPL and DPTR1=DPX1+DPH1+DPL1). This mode of operation requires