Address control register (acon), Ddress, Ontrol – Maxim Integrated High-Speed Microcontroller Users Guide: DS80C390 Supplement User Manual

Page 31: Egister, Acon)

High-Speed Microcontroller User’s Guide: DS80C390 Supplement

31 of 158

ADDRESS CONTROL REGISTER (ACON)

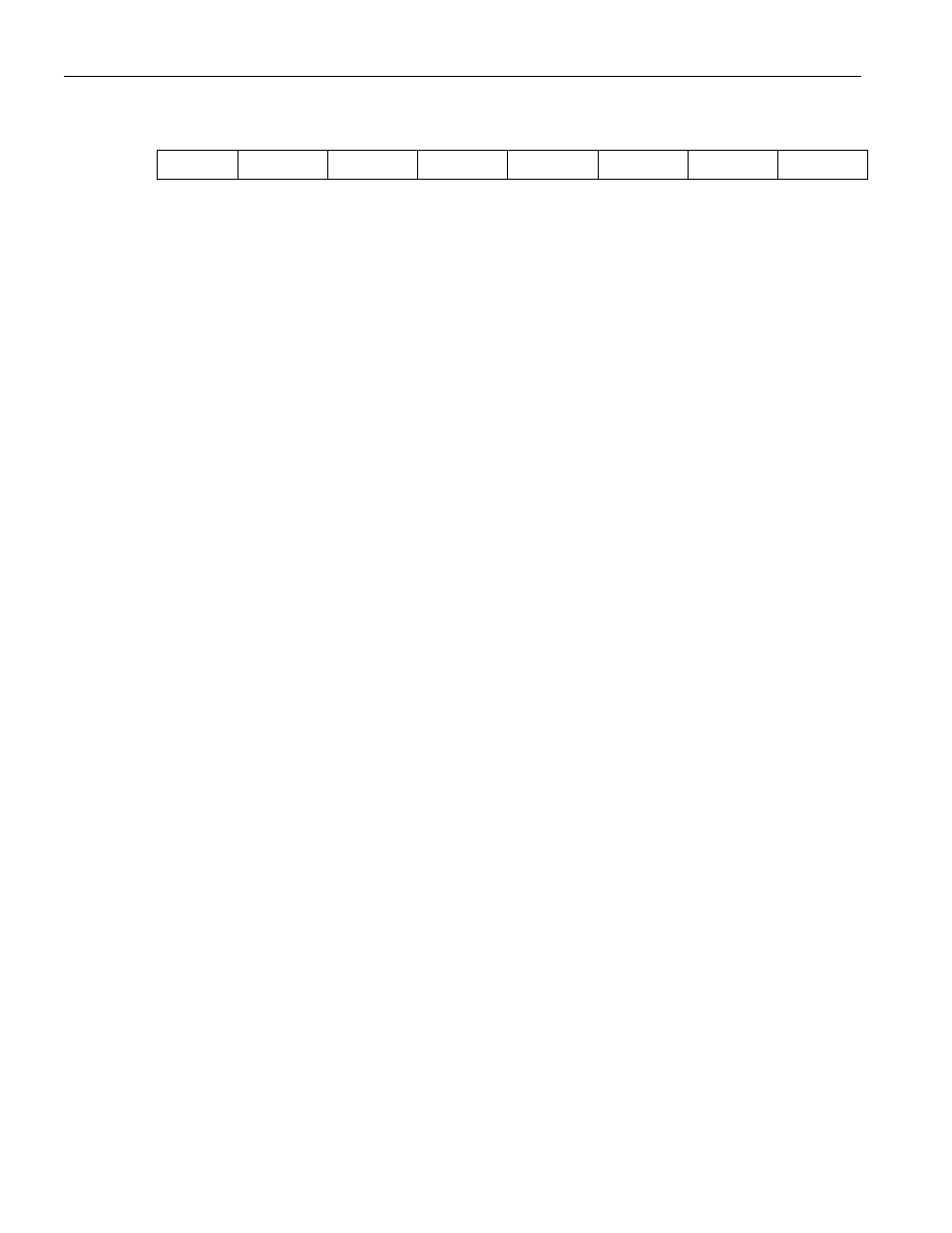

7 6 5 4 3 2 1 0

SFR

9Dh

1 1 1 1 1 SA

AM1

AM0

R-1 R-1 R-1 R-1 R-1 RT-0

RT-0

RT-0

R = Unrestricted Read, T = Timed Access Write Only, -n = Value after Reset

Bits 7-3

Reserved

SA

Bit 2

Extended Stack Address Mode Enable. This bit can only be modified by the

timed-access procedure.

0 = All instructions will utilize the traditional 8-bit 8051 stack pointer (SP;81h).

1 = All instructions will utilize the 10-bit stack pointer formed by concatenating

the 2 least significant bits of the ESP register with the SP register. Lower 1

KB of internal MOVX memory is used as the stack when this bit is set. This

bit cannot be set while IDM1:IDM0=11b.

AM1, AM0

Bits 1-0

Address Mode Control bits. These bits establish the addressing mode for the

device. These bits can only be modified by the timed-access procedure.

AM1 AM0 Addressing

Mode

0

0

16-bit Addressing Mode

0

1

22-bit Paged Addressing Mode

1

x

22-bit Contiguous Addressing Mode