Multiplier control register one (mcnt1), Ultiplier, Ontrol – Maxim Integrated High-Speed Microcontroller Users Guide: DS80C390 Supplement User Manual

Page 67: Egister, Mcnt1)

High-Speed Microcontroller User’s Guide: DS80C390 Supplement

67 of 158

MAS4-0

Bits 4-0

Multiplier Register Shift Bits. These bits determine the number of shifts

performed when a shift operation is performed with the arithmetic accelerator,

and are also used to indicate how many shifts were performed during a previous

normalization operation. These bits are cleared to 00000b following a system

reset or the initialization of the arithmetic accelerator. When these bits are cleared

to 00000b after loading the arithmetic accelerator, the device will normalize the

32-bit value loaded into the arithmetic accelerator Accumulator, rather than

shifting it. Following the normalization operation, the MAS4-0 bits will be

modified to indicate how many shifts were performed.

MAS4 MAS3 MAS2 MAS1 MAS0

Number of shifts of Arithmetic

Accelerator Accumulator

0 0 0 0 0

Normalization

0 0 0 0 1

Shift

by

1

0 0 0 1 0

Shift

by

2

0 0 0 1 1

Shift

by

3

. . . . .

.

. . . . .

.

1 1 1 1 0

Shift

by

30

1 1 1 1 1

Shift

by

31

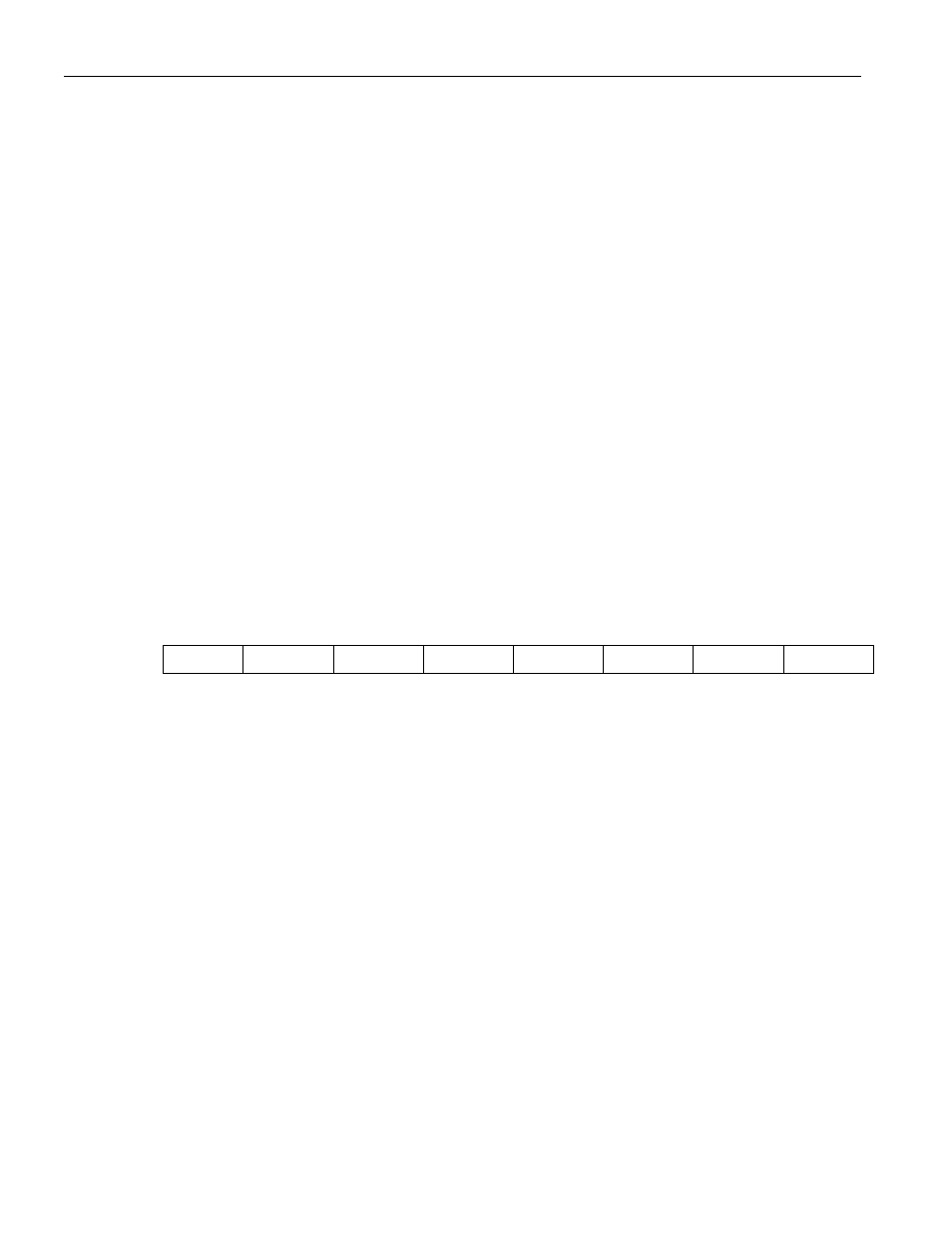

MULTIPLIER CONTROL REGISTER ONE (MCNT1)

7 6 5 4 3 2 1 0

SFR

D2h

MST

MOF

SCB

CLM

1 1 1 1

RW-0

R-0 RW-0

RW-0 R-1 R-1 R-1 R-1

R = Unrestricted Read, W = Unrestricted Read, -n = Value after Reset

MST

Bit 7

Multiply/Accumulate Status Flag. The MST bit serves as a busy flag for the

multiplier/accumulate hardware. The bit is set automatically when the processor

begins loading data into the MA or MB register, and will remain set until the

assigned task is completed. MST is automatically cleared by the multiplier/

accumulate hardware once an assigned task is completed and the results are ready

for the processor to read. MST=0 also indicates that the accelerator has been

initialized and can be loaded with new values. Clearing this bit by software from

a previous high state will terminate the current operation and initialize the

multiplier, allowing the immediate loading of new data into MA and/or MB to

perform a new calculation.

MOF

Bit 6

Multiply Overflow Flag. The MOF flag bit is cleared following a either a system

reset or the initialization of the accelerator. The MOF bit is automatically set

when the accelerator detects a divide-by-0, or when the result of the calculation is

larger than FFFFh.

SCB

Bit 5

Shift Carry Bit. The SCB bit is used as a carry bit for shift operation when SCE

bit is set to 1. Note that the SCB will not be cleared at the beginning of a new

operation and must be cleared by a write to this bit or a system reset.