Can 1 status register (c1s), Can 1 s, Tatus – Maxim Integrated High-Speed Microcontroller Users Guide: DS80C390 Supplement User Manual

Page 77: Egister, C1s)

High-Speed Microcontroller User’s Guide: DS80C390 Supplement

77 of 158

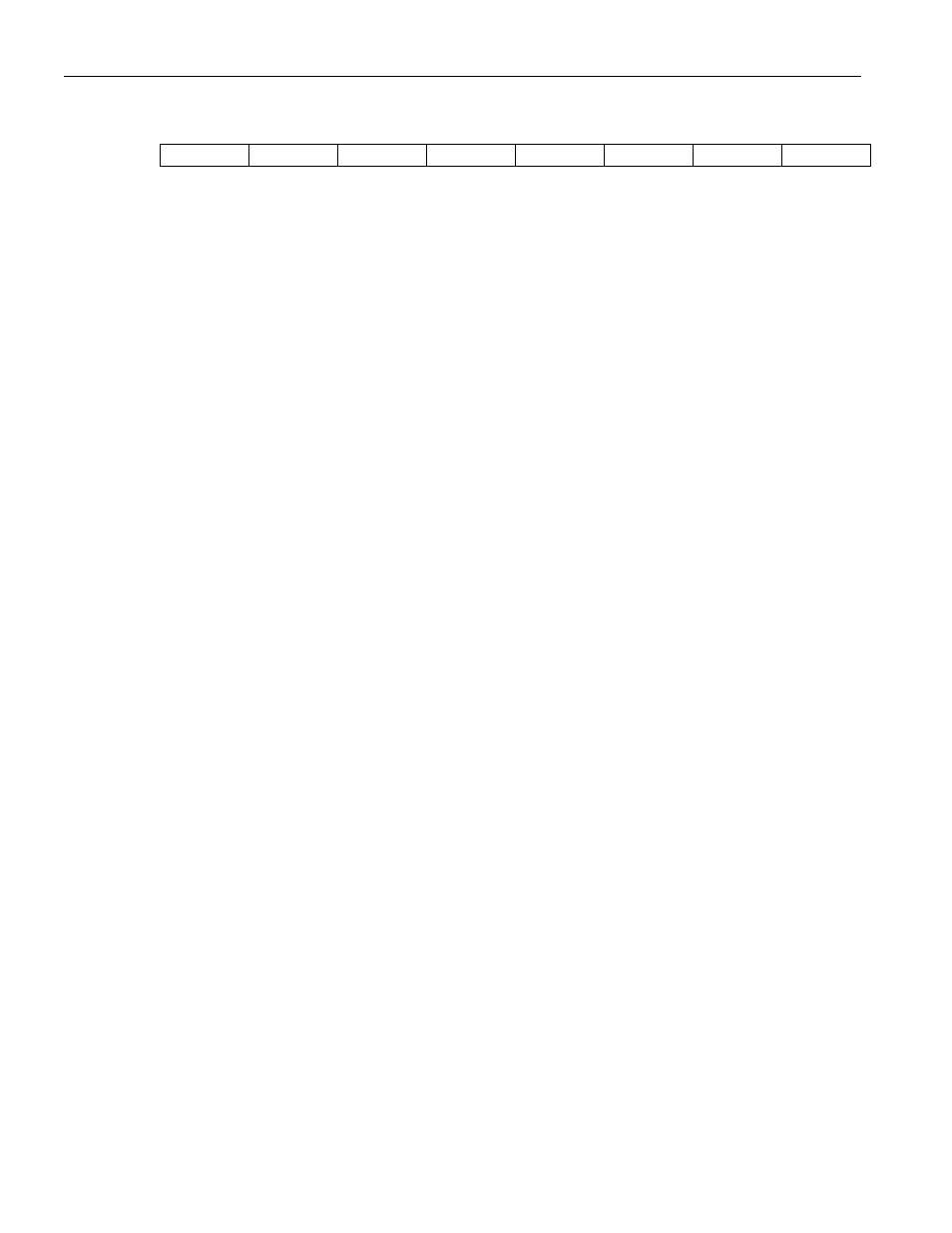

CAN 1 STATUS REGISTER (C1S)

7 6 5 4 3 2 1 0

SFR E4h

BUSOFF

CECE

WKS

RXS

TXS

ER2

ER1

ER0

R-0 R-0 R-0 RW-0

RW-0 R-0 R-0 R-0

R = Unrestricted Read, W = Unrestricted Write, -n = Value after Reset

BUSOFF

Bit 7

CAN 1 Bus Off. When BUSOFF = 1, the CAN 1 Bus is disabled and is not

capable of receiving or transmitting messages. This condition is the result of the

transmit error counter reaching a count of 256. When the CAN 1 module detects

an error count of 256 the CAN module will automatically set BUSOFF = 1 and

clear SWINT = 0.

BUSOFF is cleared to a 0 to enable CAN 1 Bus activity when the CAN processor

completes both the busoff recovery (128 X 11 consecutive recessive bits) and the

power-up sequence (11 consecutive recessive bits). Once the CAN module has

completed this relationship it will set SWINT = 1 and will enter into the software

initialization state. Once software has cleared SWINT to a 0, the CAN module

will be enabled to transmit and receive messages. When BUSOFF = 0, the CAN 1

Bus is enabled to receive or transmit messages. A change in the state of BUSOFF

from a previous 0 to a 1 will generate an interrupt if the ERIE, C1IE and IE SFR

register bits are set. All microcontroller writes to the SWINT bit are disabled

when BUSOFF = 1. Both the transmit and receive error counters are cleared to 00

hex when the Bus Off condition is cleared by the CAN module and BUSOFF is

cleared to 0.

CECE

Bit 6

CAN 1 Error Count Exceeded. This bit operates in one of two modes,

depending on the state of the ERCS bit in the CAN 1 Control Register.

ERCS = 0 (Error count limit=96) In this mode when CECE=1, the interrupt

flag indicates that either the CAN 1 Transmit Error Counter or the CAN 1

Receive Error Counter has reached an error count of 96, which represents an

exceptionally high number of errors. CECE=0 indicates that both error

counters have an error count of less than 96. A 0 to 1 transition of CECE will

generate an interrupt if the ERIE, C1IE and IE SFR bits are set.

ERCS = 1 (Error count limit=128) In this mode when CECE=1, the interrupt

flag indicates that either the CAN 1 Transmit Error Counter or the CAN 1

Receive Error Counter has reached an error count of 128, which represents an

exceptionally high number of errors. CECE = 0 indicates that the current

Transmit Error Counter and Receive Error Counter both have an error count

of less than 128. A change in the state of CECE from either a previous 0 to a

1 or from a previous 1 to 0 will generate an interrupt if the ERIE, C1IE and

IE SFR bits are set.

WKS

Bit 5

CAN 1 Wake-up Status. When WKS=1, the CAN 1 module is in power-down

mode. Clearing the PDE bit forces WKS=0. A change in the state of WKS from a

previous 1 to 0 will generate an interrupt if the STIE, C1IE and IE SFR bits are

set.

RXS

Bit 4

CAN 1 Receive Status. This bit indicates whether or not messages have been

received since the last read of the CAN 1 Status Register. RXS is only set by the

CAN 1 logic and must be cleared by the microcontroller software, the CRST bit,