Section 20: arithmetic accelerator – Maxim Integrated High-Speed Microcontroller Users Guide: DS80C390 Supplement User Manual

Page 156

High-Speed Microcontroller User’s Guide: DS80C390 Supplement

156 of 158

SECTION 20: ARITHMETIC ACCELERATOR

(DS80C390 Supplement Only)

The DS80C390 incorporates an arithmetic accelerator that performs 32- and 16-bit calculations while

maintaining 8051 software compatibility. Math operations are performed by sequentially loading three

special registers. The mathematical operation is determined by the sequence in which three dedicated

SFRs (MA, MB, and MCNT0) are accessed, eliminating the need for a special step to choose the

operation. The arithmetic accelerator has four functions: multiply, divide, shift right/left, and normalize.

The normalize function facilitates the conversion of 4-byte unsigned binary integers into floating point

format. An integral 40-bit accumulator, described later, supports multiply-and-add and divide-and-add

operations. The following table shows the operations supported by the math accelerator and their time of

execution.

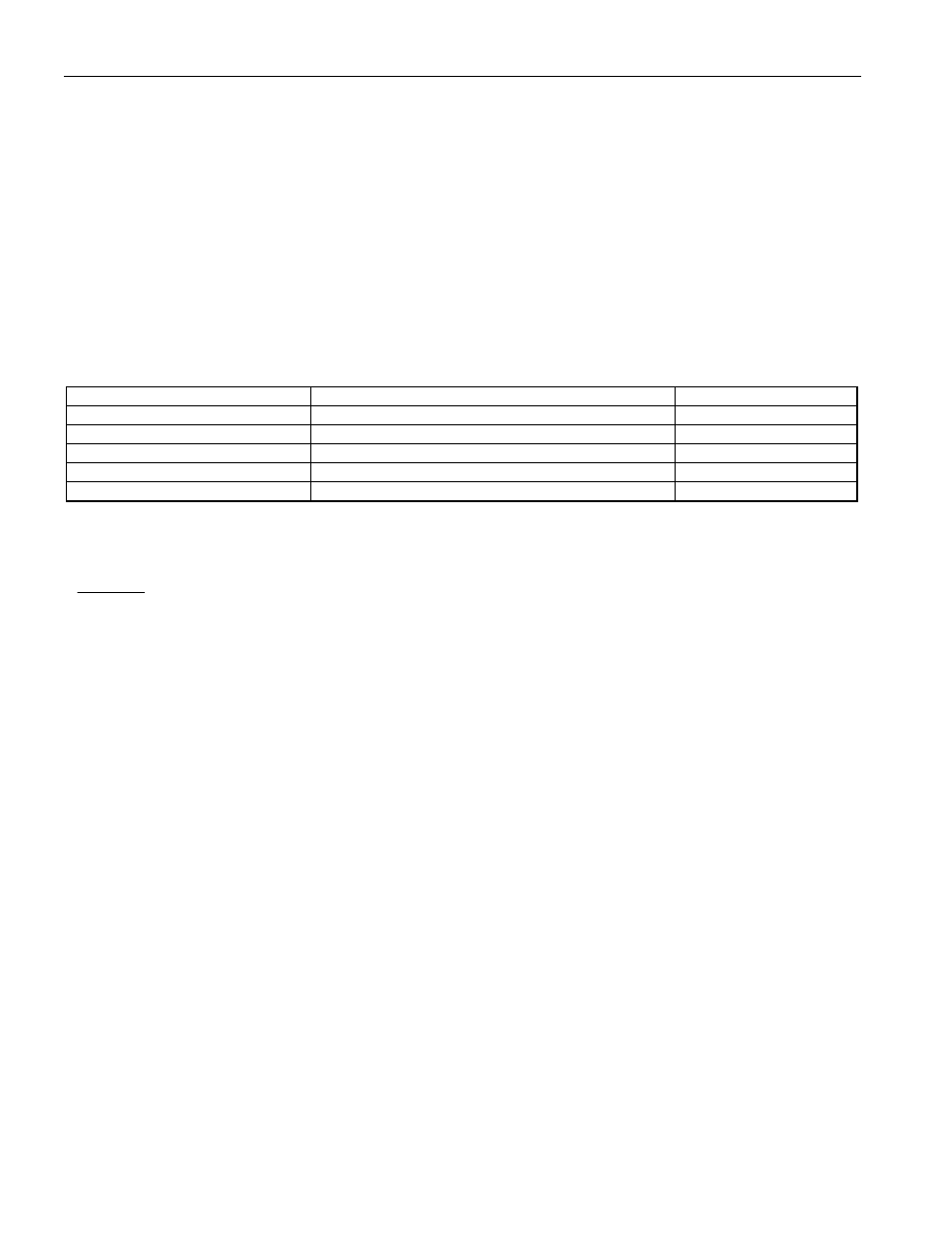

Table 20-1.

ARITHMETIC ACCELERATOR EXECUTION TIMES

OPERATION RESULT

EXECUTION

TIME

32-bit/16-bit divide

32-bit quotient, 16-bit remainder

36 t

CLCL

16-bit/16-bit divide

16-bit quotient, 16-bit remainder

24 t

CLCL

16-bit/16-bit multiply

32-bit product

24 t

CLCL

32-bit shift left/right

32-bit result

36 t

CLCL

32-bit normalize

32-bit mantissa, 5 bit exponent

36 t

CLCL

The following is a brief summary of the bits and registers used in conjunction with arithmetic acceleration

operations. Please consult the SFR listing in Section 4for a complete description of all these registers.

LSHIFT

MCNT0.7

Left Shift. This bit determines whether shift operations proceed from LSb to MSb or

vice versa.

CSE

MCNT0.6

Circular Shift Enable. This bit determines whether shift operations will wrap between

the LSb and MSb.

SCE

MCNT0.5

Shift Carry Enable. This bit determines whether the arithmetic accelerator carry bit is

included in the shift process.

MAS4-0

MCNT0.4-0.

Multiplier Register Shift Bits. When performing a shift operation, these bits

determine how many shifts to perform. Following a normalize operation, these bits will

contain indicate the number shifts performed.

MST

MCNT1.7

Multiply/Accumulate Status Flag. This bit serves as a busy flag for the arithmetic

accumulator operations.

MOF

MCNT1.6

Multiply Overflow Flag. This bit is set when a divide-by-0 or when the result of a

calculation exceeds FFFFh.

SCB

MCNT1.5

Shift Carry Bit. This bit serves as the carry bit during arithmetic accelerator shift

operations when SCE=1. This bit must be cleared (or set) by software as desired before

each new shift operation.

CLM

MCNT1.4

Clear Accelerator Registers. Setting this bit clears the MA, MB, and MC registers.

MA

MA.7-0

Multiplier A Register. This register is used as both a source and result register for

various arithmetic accelerator functions.

MB

MB.7-0

Multiplier B Register. This register is used as both a source and result register for

various arithmetic accelerator functions.

MC

MC.7-0

Multiplier C Register. This register serves as the 40-bit accumulator of the arithmetic

accelerator.