Port 2 (p2), Port 5 (p5), 2 (p2) – Maxim Integrated High-Speed Microcontroller Users Guide: DS80C390 Supplement User Manual

Page 34: 5 (p5)

High-Speed Microcontroller User’s Guide: DS80C390 Supplement

34 of 158

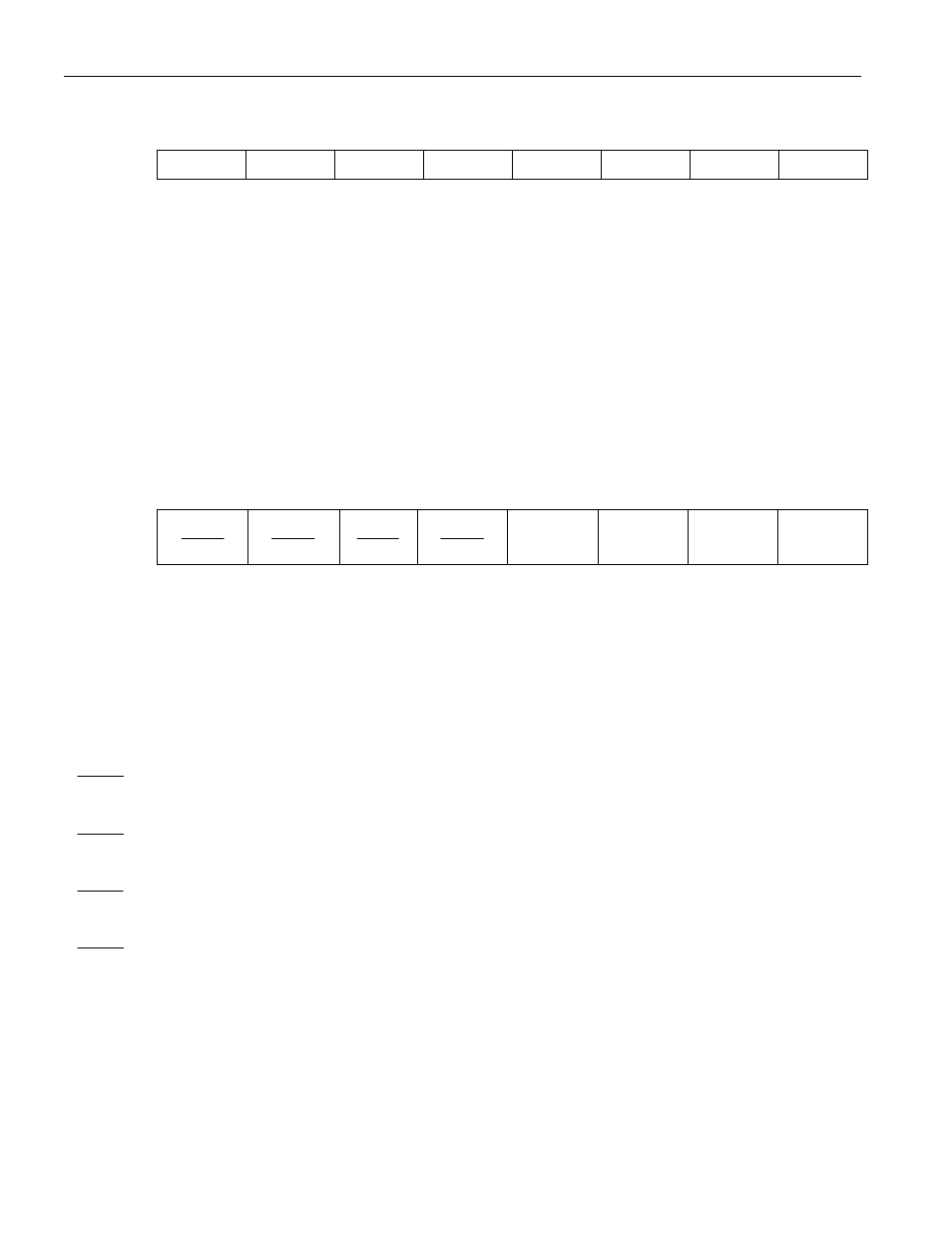

PORT 2 (P2)

7 6 5 4 3 2 1 0

SFR A0h A15/P2.7 A14/P2.6 A13/P2.5 A12/P2.4 A11/P2.3 A10/P2.2 A9/P2.1 A8/P2.0

RW-1 RW-1 RW-1 RW-1 RW-1 RW-1 RW-1 RW-1

R = Unrestricted Read, W = Unrestricted Write, -n = Value after Reset

P2.7-0

Bits 7-0

Port 2. The Port 2 pins function as an address bus during external memory

accesses, and a general-purpose I/O port when executing code memory from the

internal 4kB SRAM (IDM1,IDM0 = 00b). When executing programs from the

internal 4kB SRAM, the contents of this SFR will be driven onto the Port 2 pins.

When executing programs from external memory, writes to P2 will have no affect

on the state of the Port 2 pins (except during register-indirect MOVX operations).

When executing register-indirect instructions such as MOVX A, @R1, this

register supplies the address MSB during data memory operations.

PORT 5 (P5)

7 6 5 4 3 2 1 0

SFR A1h

P5.7

PCE3

P5.6

PCE2

P5.5

PCE1

P5.4

PCE0

P5.3

C1TX

P5.2

C1RX

P5.1

C0RX

P5.0

C0TX

RW-1 RW-1 RW-1 RW-1 RW-1 RW-1 RW-1 RW-1

R = Unrestricted Read, W = Unrestricted Write, -n = Value after Reset

General Purpose I/O Port 5. This register functions as a general purpose

I/O port. In addition, all the pins have an alternate function listed below.

Each of the alternate functions is controlled by and/or influences other SFRs.

The associated Port 5 latch bit must contain a logic one before the pin can be

used in its alternate function capability.

PCE3

Bit 7

Peripheral Chip Enable 3. When enabled by the P5CNT register, this pin

will assert the fourth chip enable signal.

PCE2

Bit 6

Peripheral Chip Enable 2. When enabled by the P5CNT register, this pin

will assert the third chip enable signal.

PCE1

Bit 5

Peripheral Chip Enable 1. When enabled by the P5CNT register, this pin

will assert the second chip enable signal.

PCE0

Bit 4

Peripheral Chip Enable 0. When enabled by the P5CNT register, this pin

will assert the first chip enable signal.

C1TX/TXD1

Bit 3

CAN 1 Transmit/Serial Port 1 Transmit. This pin is connected to the

transmit data input pin of the CAN 1 transceiver device. Setting the Serial

Port 1 External Connection bit (SP1EC, P5CNT.5) configures this pin as the

Serial Port 1 transmit signal, disabling the corresponding CAN 1 function.

C1RX/RXD1

Bit 2

CAN 1 Receive/Serial Port 1 Receive. This pin is connected to the receive

data output pin of the CAN 1 transceiver device. Setting the Serial Port 1