Watchdog control (wdcon), Wdif, Atchdog – Maxim Integrated High-Speed Microcontroller Users Guide: DS80C390 Supplement User Manual

Page 71: Ontrol, Wdcon)

High-Speed Microcontroller User’s Guide: DS80C390 Supplement

71 of 158

WATCHDOG CONTROL (WDCON)

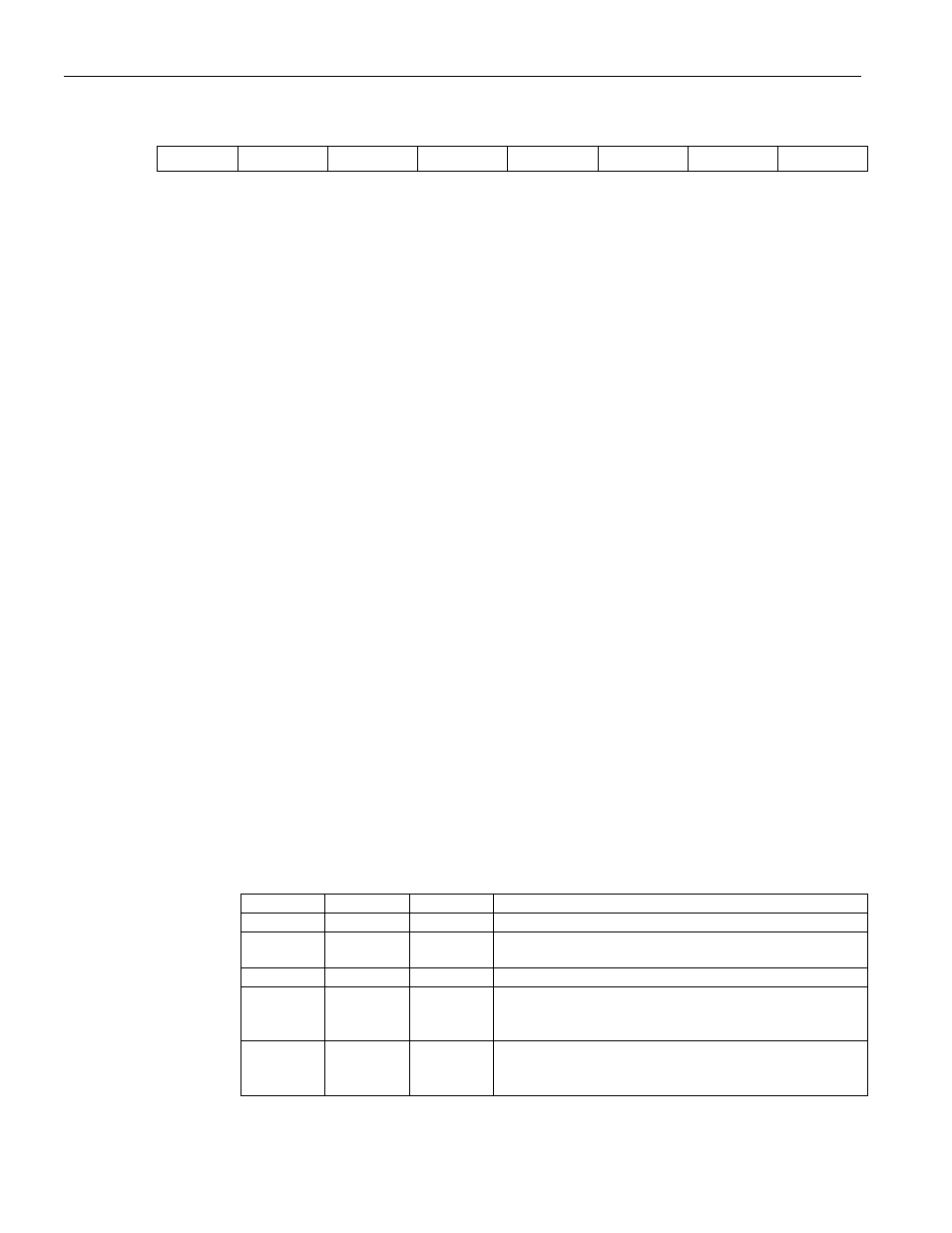

7 6 5 4 3 2 1 0

SFR D8h

SMOD

POR

EPF1

PFI

WDIF

WTRF

EWT

RWT

RW-0 RT-* RW-0 RW-* RT-0 RW-* RT-* RT-0

R = Unrestricted Read, W = Unrestricted Write, T = Timed Access Write Only, -n = Value after Reset, * = See Description

SMOD

Bit 7

Serial Modification. This bit controls the doubling of the serial port 1 baud rate

in modes 1, 2, and 3. This bit is ignored when RCLK = 1 or TCLK = 1.

0 = Serial port 1 baud rate operates at normal speed

1 = Serial port 1 baud rate is doubled.

POR

Bit 6

Power-on Reset Flag. This bit indicates whether the last reset was a power-on

reset. This bit is typically interrogated following a reset to determine if the reset

was caused by a power-on reset. It must be cleared by a Timed Access write

before the next reset of any kind or the software may erroneously determine that

another power-on reset has occurred. This bit is set following a power-on reset

and unaffected by all other resets.

0 = Last reset was from a source other than a power-on reset

1 = Last reset was a power-on reset.

EPFI

Bit 5

Enable Power fail Interrupt. This bit enables/disables the ability of the internal

band-gap reference to generate a power-fail interrupt when V

CC

falls below

approximately 4.5 volts. While in Stop mode, both this bit and the Band-gap

Select bit, BGS (EXIF.0), must be set to enable the power-fail interrupt.

0 = Power-fail interrupt disabled.

1 = Power-fail interrupt enabled during normal operation. Power-fail interrupt

enabled in Stop mode if BGS is set.

PFI

Bit 4

Power-Fail Interrupt Flag. When set, this bit indicates that a power-fail

interrupt has occurred. This bit must be cleared in software before exiting the

interrupt service routine, or another interrupt will be generated. Setting this bit in

software will generate a power-fail interrupt, if enabled.

WDIF

Bit 3

Watchdog Interrupt Flag. This bit, in conjunction with the Watchdog Timer

Interrupt Enable bit, EWDI (EIE.4), and Enable Watchdog Timer Reset bit

(WDCON.1), indicates if a watchdog timer event has occurred and what action

will be taken. This bit must be cleared in software before exiting the interrupt

service routine, or another interrupt will be generated. Setting this bit in software

will generate a watchdog interrupt if enabled. This bit can only be modified using

a timed-access procedure.

EWT EWDI WDIF

RESULT

X

X

0

No watchdog event has occurred.

0 0 1

Watchdog time-out has expired. No interrupt has been

generated.

0 1 1

Watchdog

interrupt

has

occurred.

1 0 1

Watchdog time-out has expired. No interrupt has been

generated. Watchdog timer reset will occur in 512 cycles

if RWT is not strobed.

1 1 1

Watchdog interrupt has occurred. Watchdog timer reset

will occur in 512 cycles if RWT is not set using a Timed

Access procedure.