Serial port 0 control (scon0), Ren_0, Erial – Maxim Integrated High-Speed Microcontroller Users Guide: DS80C390 Supplement User Manual

Page 28: Ontrol, Scon0)

High-Speed Microcontroller User’s Guide: DS80C390 Supplement

28 of 158

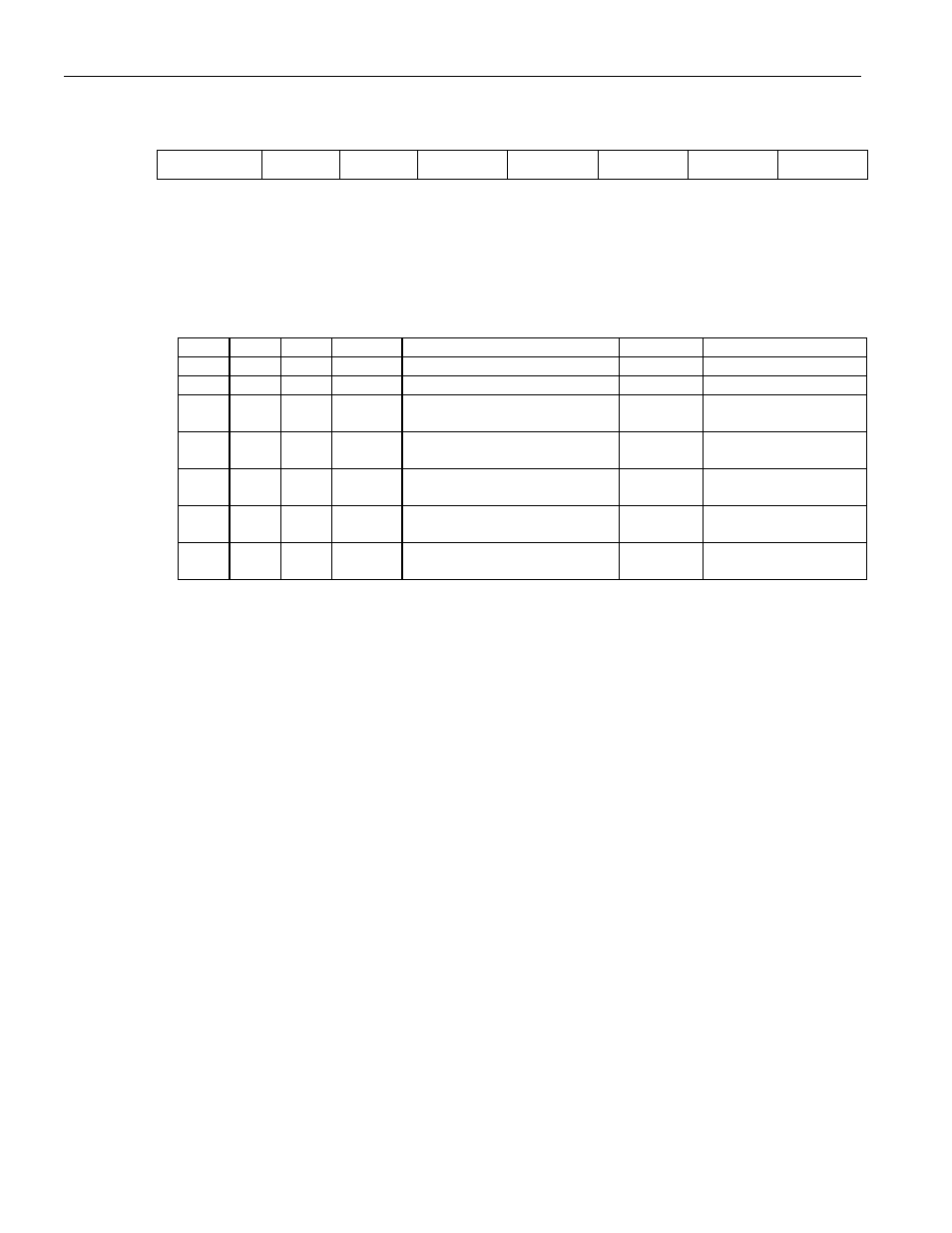

SERIAL PORT 0 CONTROL (SCON0)

7 6

5 4 3 2 1 0

SFR 98h SM0/FE_0 SM1_0 SM2_0

REN_0

TB8_0

RB8_0

T1_0

R1_0

RW-0 RW-0

RW-0 RW-0 RW-0 RW-0 RW-0 RW-0

R = Unrestricted Read, W = Unrestricted Write, -n = Value after Reset

SM0-2

Bits 7-5

Serial Port Mode. These bits control the mode of serial port 0. In addition the

SM0 and SM2_0 bits have secondary functions as shown below.

SM0 SM1 SM2 MODE

FUNCTION LENGTH

PERIOD

0 0 0 0

Synchronous

8

bits

12

t

CLK

0 0 1 0

Synchronous

8

bits

4

t

CLK

0 1 X 1

Asynchronous

10

bits

Timer 1 or 2

baud rate equation

1 0 0 2

Asynchronous

11

bits 64 t

CLK

(SMOD=0)

32 t

CLK

(SMOD=1)

1 0 1 2

Asynchronous w/

Multiprocessor communication

11 bits

64 t

CLK

(SMOD=0)

32 t

CLK

(SMOD=1)

1 1 0 3

Asynchronous

11

bits

Timer 1 or 2

baud rate equation

1 1 1 3

Asynchronous w/

Multiprocessor communication

11 bits

Timer 1 or 2

baud rate equation

SM0/FE_0

Bit 7

Framing Error Flag. When SMOD0 (PCON.6)=0, this bit (SM0) is used to

select the mode for serial port 0. When SMOD0 (PCON.6)=1, this bit (FE) will

be set upon detection of an invalid stop bit. When used as FE, this bit must be

cleared in software. Once the SMOD0 bit is set, modifications to this bit will not

affect the serial port mode settings. Although accessed from the same register,

internally the data for bits SM0 and FE are stored in different locations.

SM1_0

Bit 6

No alternate function.

SM2_0

Bit 5

Multiple CPU Communications. The function of this bit is dependent on the

serial port 0 mode.

Mode 0: Selects 12 t

CLK

or 4 t

CLK

period for synchronous serial port 0 data

transfers.

Mode 1: When set, reception is ignored (RI_0 is not set) if invalid stop bit

received.

Mode 2/3: When this bit is set, multiprocessor communications are enabled in

modes 2 and 3. This will prevent the RI_0 bit from being set, and an

interrupt being asserted, if the 9

th

bit received is not 1.

REN_0

Bit 4

Receiver Enable. This bit enable/disables the serial port 0 receiver shift register.

0 = Serial port 0 reception disabled.

1= Serial port 0 receiver enabled (modes 1, 2, 3). Initiate synchronous reception

(mode 0).