Multiplier control register zero (mcnt0), Ultiplier, Ontrol – Maxim Integrated High-Speed Microcontroller Users Guide: DS80C390 Supplement User Manual

Page 66: Egister, Mcnt0)

High-Speed Microcontroller User’s Guide: DS80C390 Supplement

66 of 158

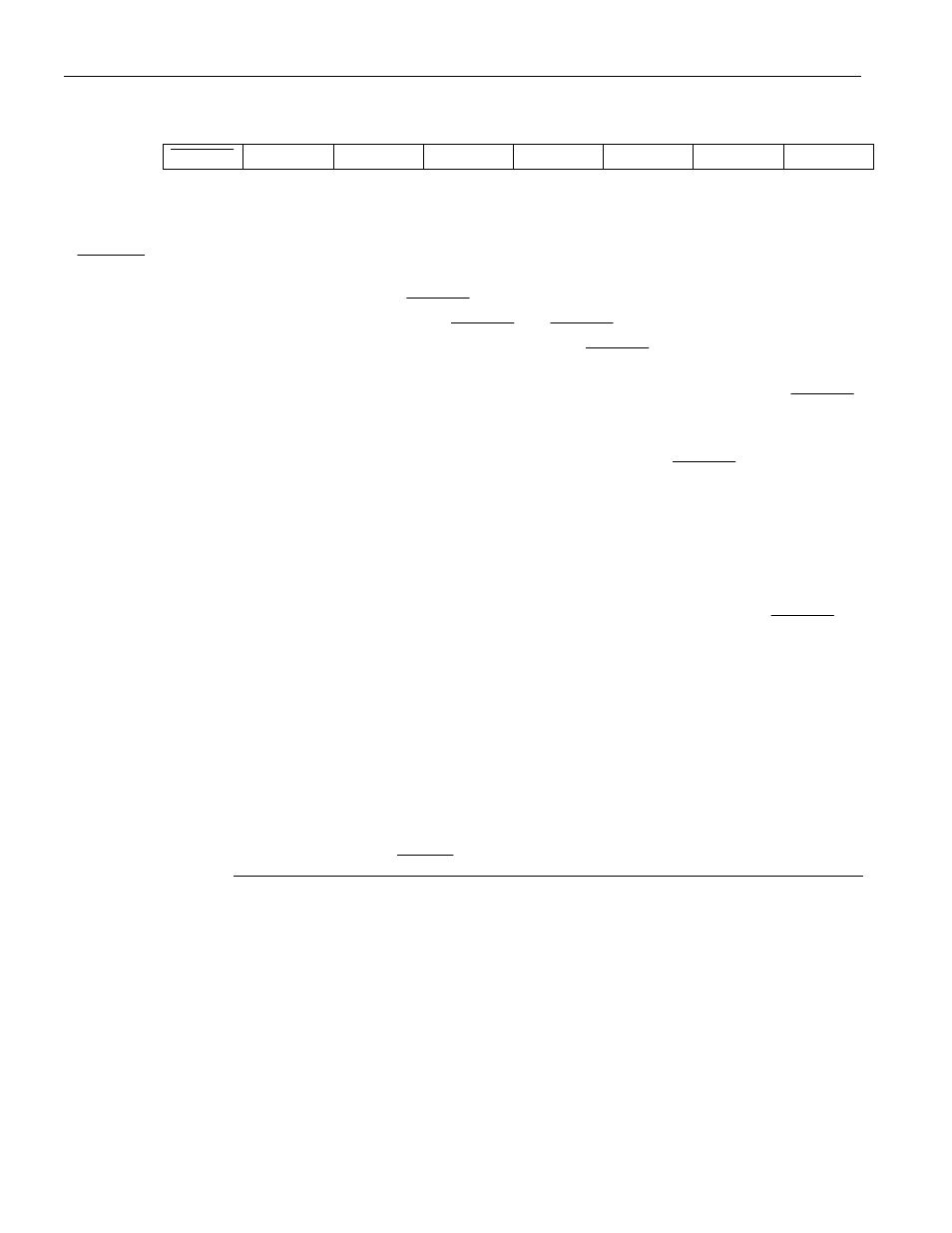

MULTIPLIER CONTROL REGISTER ZERO (MCNT0)

7 6 5 4 3 2 1 0

SFR D1h

LSHIFT

CSE SCE MAS4 MAS3 MAS2 MAS1 MAS0

RW-0 RW-0 RW-0 RW-0 RW-0 RW-0 RW-0 RW-0

R = Unrestricted Read, W = Unrestricted Read, -n = Value after Reset

LSHIFT

Bit 7

Left Shift. This bit works in conjunction with the SCE and CSE bits to

determine the direction and path of arithmetic accelerator shift operations as

shown below. When LSHIFT =0, shift operations will shift from the LSb to the

MSb, and vice versa when LSHIFT =1. LSHIFT does not alter any other type of

calculation other than the shift function. The LSHIFT bit is cleared to 0 following

a either a system reset or the initialization of the accelerator.

CSE

Bit 6

Circular Shift Enable. This bit works in conjunction with the SCE and LSHIFT

bits to determine the direction and path of arithmetic accelerator shift operations

as shown below. When CSE=1, shifts of the arithmetic accelerator will wrap bit

31 to bit 0 or vice versa depending on the settings of the LSHIFT bits. When

CSE is cleared to a 0, all left or right shifts will shift cleared bit values into the

most significant bit for a right shift and the least significant bit for a left shift.

When CSE is set to a 1 and SCB is set to a 1, the most significant bit will be

shifted into the 32 Bit Carry Bit when doing a left shift and least most significant

bit will be shifted into the 32 Bit Carry Bit when doing a right shift. The CSE bit

is cleared to 0 following a system reset.

SCE

Bit 5

Shift Carry Enable. This bit works in conjunction with the CSE and LSHIFT

bits to determine the direction and path of arithmetic accelerator shift operations

as shown below. When SCE=1 the arithmetic accelerator carry bit will be shifted

into the LSb for a left shift and into the MSb for a right shift. When SCE=0, shifts

will not incorporate the arithmetic accelerator carry bit as a part of the shifting

process. If CSE=0 the arithmetic accelerator carry bit will remain unchanged

during the shift process. If CSE=1 the MSb will be shifted into the carry bit on a

left shift and the least most significant bit of the arithmetic accelerator will be

shifted into the carry bit on a right shift. The SCE bit is cleared to 0 following a

system reset.

Arithmetic Accelerator Values After Shift

SCE CSE

LSHIFT

MSb (bit 31)

LSb (bit 0)

Carry bit

0

0

0

Previous bit 30 Previous bit 0

unchanged

0 0 1

0 Previous

bit

1

unchanged

0

1

0

Previous bit 30 Previous bit 31

unchanged

0

1

1

Previous bit 0

Previous bit 1

unchanged

1

0

0

Previous bit 30 Previous carry

unchanged

1

0

1

Previous carry

Previous bit 1

unchanged

1 1 0

Previous

bit

30

Previous carry Previous bit 31

1 1 1

Previous

carry

Previous bit 1

Previous bit 0