The 2-wire serial interface status register - twsr, The 2-wire serial interface data register - twdr, Atmega163(l) – Rainbow Electronics ATmega163L User Manual

Page 71

ATmega163(L)

71

The TWCR is used to control the operation of the 2-wire Serial Interface. It is used to enable the 2-wire Serial Interface, to

initiate a master access by applying a START condition to the bus, to generate a receiver acknowledge, to generate a stop

condition, and to control halting of the bus while the data to be written to the bus are written to the TWDR. It also indicates

a write collision if data is attempted written to TWDR while the register is inaccessible.

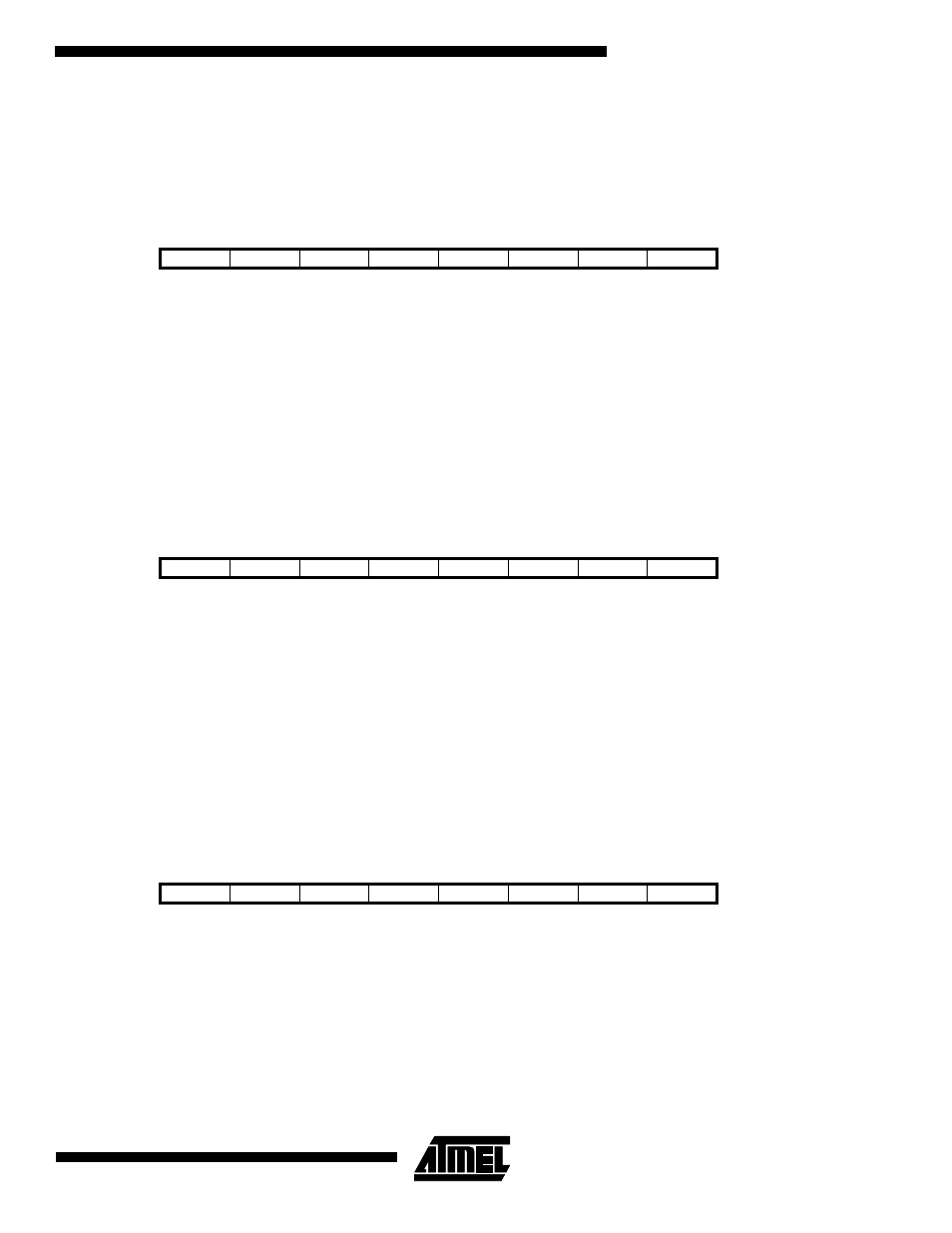

The 2-wire Serial Interface Status Register - TWSR

•

Bits 7..3 - TWS: 2-wire Serial Interface Status

These 5 bits reflect the status of the 2-Wire Serial Interface logic and the 2-wire Serial Bus.

•

Bits 2..0 - Res: Reserved bits

These bits are reserved in ATmega163 and will always read as zero

The TWSR is read only. It contains a status code which reflects the status of the 2-wire Serial Interface logic and the 2-wire

Serial Bus. There are 26 possible status codes. When TWSR contains $F8, no relevant state information is available and

no 2-wire Serial Interface interrupt is requested. A valid status code is available in TWSR one CPU clock cycle after the 2-

wire Serial Interface interrupt flag (TWINT) is set by hardware and is valid until one CPU clock cycle after TWINT is cleared

by software. Table 32 to Table 36 give the status information for the various modes.

The 2-wire Serial Interface Data Register - TWDR

•

Bits 7..0 - TWD: 2-Wire Serial Interface Data Register

These eight bits constitute the next data byte to be transmitted, or the latest data byte received on the 2-wire Serial Bus.

In transmit mode, TWDR contains the next byte to be transmitted. In receive mode, the TWDR contains the last byte

received. It is writeable while the 2-wire Serial Interface is not in the process of shifting a byte. This occurs when the 2-wire

Serial Interface interrupt flag (TWINT) is set by hardware. Note that the data register cannot be initialized by the user before

the first interrupt occurs. The data in TWDR remain stable as long as TWINT is set. While data is shifted out, data on the

bus is simultaneously shifted in. TWDR always contains the last byte present on the bus, except after a wake up from ADC

Noise Reduction Mode, Power Down Mode, or Power Save Mode by the 2-wire Serial Interface interrupt. For example, in

the case of a lost bus arbitration, no data is lost in the transition from Master to Slave. Handling of the ACK flag is controlled

automatically by the 2-wire Serial Interface logic, the CPU cannot access the ACK bit directly.

The 2-wire Serial Interface (Slave) Address Register - TWAR

•

Bits 7..1 - TWA: 2-wire Serial Interface (Slave) Address Register

These seven bits constitute the slave address of the 2-wire Serial Bus unit.

•

Bit 0 - TWGCE: 2-wire Serial Interface General Call Recognition Enable bit

This bit enables, if set, the recognition of the General Call given over the 2-wire Serial Bus.

The TWAR should be loaded with the 7-bit slave address (in the seven most significant bits of TWAR) to which the 2-wire

Serial Interface will respond when programmed as a slave transmitter or receiver, and not needed in the master modes.

The LSB of TWAR is used to enable recognition of the general call address ($00). There is an associated address compar-

Bit

7

6

5

4

3

2

1

0

$01 ($21)

TWS7

TWS6

TWS5

TWS4

TWS3

-

-

-

TWSR

Read/Write

R

R

R

R

R

R

R

R

Initial value

1

1

1

1

1

0

0

0

Bit

7

6

5

4

3

2

1

0

$03 ($23)

TWD7

TWD6

TWD5

TWD4

TWD3

TWD2

TWD1

TWD0

TWDR

Read/Write

R/W

R/W

R/W

R/W

R/W

R/W

R/W

R/W

Initial value

1

1

1

1

1

1

1

1

Bit

7

6

5

4

3

2

1

0

$02 ($22)

TWA6

TWA5

TWA4

TWA3

TWA2

TWA1

TWA0

TWGCE

TWAR

Read/Write

R/W

R/W

R/W

R/W

R/W

R/W

R/W

R/W

Initial value

1

1

1

1

1

1

1

0