Sleep modes, Idle mode, Adc noise reduction mode – Rainbow Electronics ATmega163L User Manual

Page 31: Power-down mode, Atmega163(l)

ATmega163(L)

31

Sleep Modes

To enter any of the four sleep modes, the SE bit in MCUCR must be set (one) and a SLEEP instruction must be executed.

The SM1 and SM0 bits in the MCUCR register select which sleep mode (Idle, ADC Noise Reduction, Power Down, or

Power Save) will be activated by the SLEEP instruction. See Table 7 for a summary. If an enabled interrupt occurs while

the MCU is in a sleep mode, the MCU wakes up. The MCU is then halted for four cycles, executes the interrupt routine, and

resumes execution from the instruction following SLEEP. The contents of the register file, SRAM, and I/O memory are unal-

tered when the device wakes up from sleep. If a reset occurs during sleep mode, the MCU wakes up and executes from the

Reset vector.

Idle Mode

When the SM1/SM0 bits are set to 00, the SLEEP instruction makes the MCU enter Idle Mode, stopping the CPU but allow-

ing SPI, UART, Analog Comparator, ADC, 2-wire Serial Interface, Timer/Counters, Watchdog, and the interrupt system to

continue operating (if enabled). This enables the MCU to wake up from external triggered interrupts as well as internal ones

like the Timer Overflow and UART Receive Complete interrupts. If wake-up from the Analog Comparator interrupt is not

required, the Analog Comparator can be powered down by setting the ACD bit in the Analog Comparator Control and Sta-

tus register - ACSR. This will reduce power consumption in Idle Mode. If the ADC is enabled, a conversion starts

automatically when this mode is entered.

ADC Noise Reduction Mode

When the SM1/SM0 bits are set to 01, the SLEEP instruction makes the MCU enter ADC Noise Reduction Mode, stopping

the CPU but allowing the ADC, the external interrupts, the 2-wire Serial Interface address watch, Timer/Counter2 and the

Watchdog to continue operating (if enabled). This improves the noise environment for the ADC, enabling higher resolution

measurements. If the ADC is enabled, a conversion starts automatically when this mode is entered. Apart from the ADC

Conversion Complete interrupt, only an external reset, a watchdog reset (if enabled), a brown-out reset, a 2-wire Serial

Interface address match interrupt, or an external level interrupt can wake up the MCU from ADC Noise Reduction Mode.A

Timer/Counter2 output compare or overflow event will wake up the MCU, but will not generate an interrupt unless

Timer/Counter2 is clocked asynchronously.

In future devices this is subject to change. It is recommended for future code compability to disable Timer/Counter2 inter-

rupts during ADC Noise Reduction mode if the Timer/Counter2 is clocked synchronously.

Power-down Mode

When the SM1/SM0 bits are 10, the SLEEP instruction makes the MCU enter Power Down Mode. In this mode, the exter-

nal oscillator is stopped, while the external interrupts, the 2-wire Serial Interface address match, and the Watchdog

continue operating (if enabled). Only an external reset, a watchdog reset, a brown-out reset, a 2-wire Serial Interface

address match interrupt, or an external level interrupt can wake up the MCU.

Note that if a level triggered interrupt is used for wake-up from Power Down Mode, the changed level must be held for

some time to wake up the MCU. This makes the MCU less sensitive to noise. The changed level is sampled twice by the

watchdog oscillator clock, and if the input has the required level during this time, the MCU will wake up. The period of the

watchdog oscillator is 1 µs (nominal) at 5.0V and 25

°C. The frequency of the watchdog oscillator is voltage dependent as

shown in the Electrical Characteristics section.

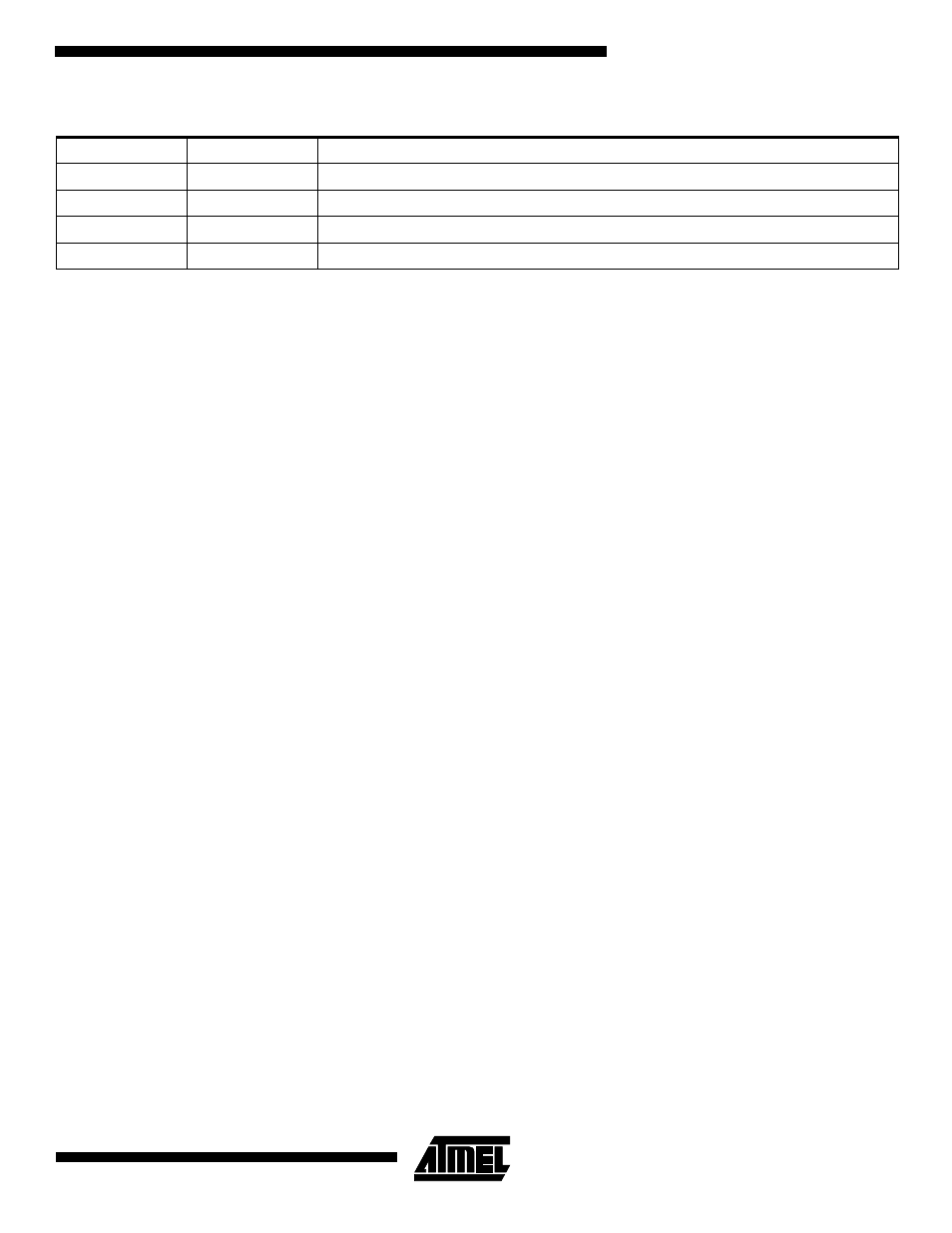

Table 9. Interrupt 0 Sense Control

ISC01

ISC00

Description

0

0

The low level of INT0 generates an interrupt request.

0

1

Any logical change on INT0 generates an interrupt request.

1

0

The falling edge of INT0 generates an interrupt request.

1

1

The rising edge of INT0 generates an interrupt request.