Program and data memory lock bits, Fuse bits, Atmega163(l) – Rainbow Electronics ATmega163L User Manual

Page 123

ATmega163(L)

123

rjmp

Wait_spm

ret

Program And Data Memory Lock Bits

The ATmega163 provides six Lock bits which can be left unprogrammed (‘1’) or can be programmed (‘0’) to obtain the addi-

tional features listed in Table 54. The Lock bits can only be erased to ‘1’ with the Chip Erase command.

Note:

1. Program the Fuse bits before programming the Lock bits.

Fuse Bits

The ATmega163 has ten Fuse bits, divided in two groups. The Fuse High bits are BOOTSZ1..0 and BOOTRST, and the

Fuse Low bits are BODLEVEL, BODEN, SPIEN, and CKSEL3..0.

• BOOTSZ1..0 select the size and start address of the Boot Flash section according to Table 50 on page 115. Default

value is ‘11’ (both unprogrammed).

• When BOOTRST is programmed (‘0’), the reset vector is set to the start address of the Boot Flash section, as selected

by the BOOTSZ fuses according to Table 50 on page 115. If the BOOTRST is unprogrammed (‘1’), the reset vector is set

to address $0000. Default value is unprogrammed (‘1’).

• The BODLEVEL Fuse selects the Brown-out Detection Level and changes the Start-up times, according to Table 4 on

page 22 and Table 5 on page 22, respectively. Default value is unprogrammed (‘1’).

• When the BODEN Fuse is programmed (‘0’), the Brown-out Detector is enabled. See “Reset and Interrupt Handling” on

page 19. Default value is unprogrammed (‘1’).

• When the SPIEN Fuse is programmed (‘0’), Serial Program and Data Downloading are enabled. Default value is

programmed (‘0’). The SPIEN Fuse is not accessible in serial programming mode.

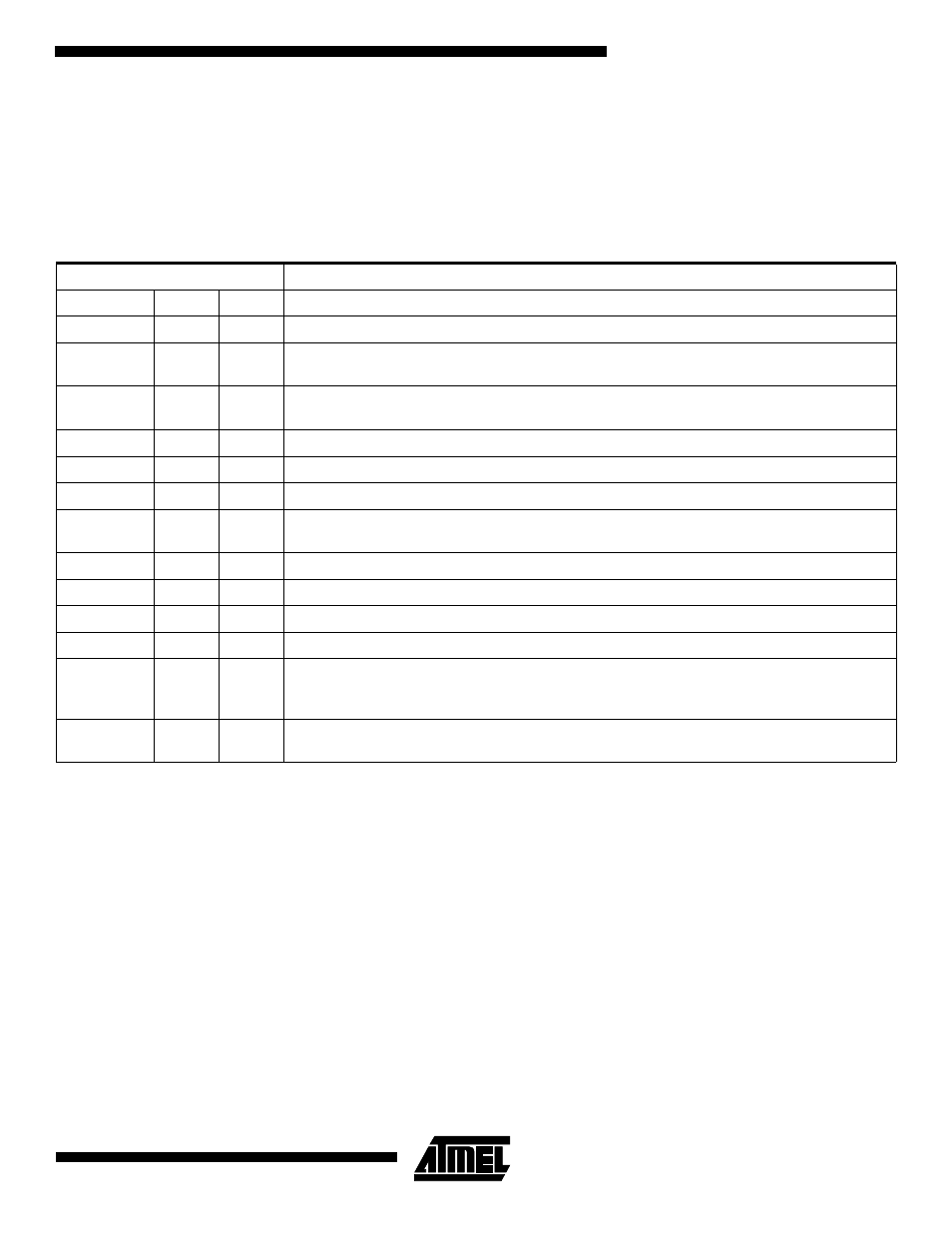

Table 54. Lock Bit Protection Modes

Memory Lock Bits

Protection Type

LB mode

LB1

LB2

1

1

1

No memory lock features enabled for parallel and serial programming.

2

0

1

Further programming of the Flash and EEPROM is disabled in parallel and serial programming

mode. The Fuse bits are locked in both serial and parallel programming mode.

3

0

0

Further programming and verification of the Flash and EEPROM is disabled in parallel and serial

programming mode. The Fuse bits are locked in both serial and parallel programming mode.

BLB0 mode

BLB01

BLB02

1

1

1

No restrictions for SPM, LPM accessing the Application section.

2

0

1

SPM is not allowed to write to the Application section.

3

0

0

SPM is not allowed to write to the Application section, and LPM executing from the Boot Loader

section is not allowed to read from the Application section.

4

1

0

LPM executing from the Boot Loader section is not allowed to read from the Application section.

BLB1 mode

BLB11

BLB12

1

1

1

No restrictions for SPM, LPM accessing the Boot Loader section.

2

0

1

SPM is not allowed to write to the Boot Loader section.

3

0

0

SPM is not allowed to write to the Boot Loader section, and LPM executing from the Application

section is not allowed to read from the Boot Loader section. If code executed from the Boot

Section, the interrupts are disabled when BLB12 is programmed.

4

1

0

LPM executing from the Application section is not allowed to read from the Boot Loader section.

If code executed from the Boot Section, the interrupts are disabled when BLB12 is programmed.