I/o memory, Figure 23, Atmega163(l) – Rainbow Electronics ATmega163L User Manual

Page 16

ATmega163(L)

16

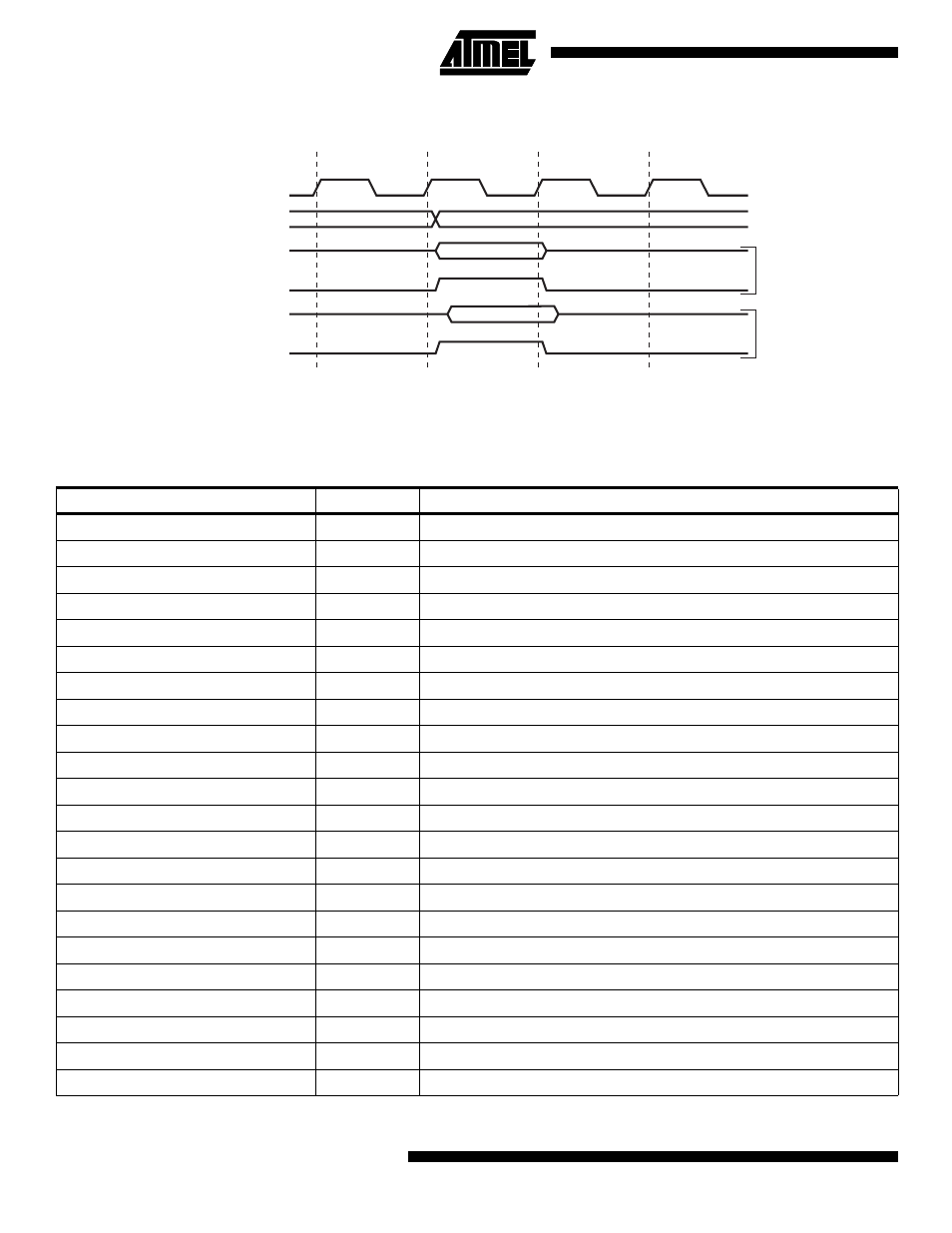

Figure 23. On-chip Data SRAM Access Cycles

I/O Memory

The I/O space definition of the ATmega163 is shown in the following table:

Table 2. ATmega163 I/O Space

I/O Address (SRAM Address)

Name

Function

$3F ($5F)

SREG

Status REGister

$3E ($5E)

SPH

Stack Pointer High

$3D ($5D)

SPL

Stack Pointer Low

$3B ($5B)

GIMSK

General Interrupt MaSK Register

$3A ($5A)

GIFR

General Interrupt Flag Register

$39 ($59)

TIMSK

Timer/Counter Interrupt MaSK Register

$38 ($58)

TIFR

Timer/Counter Interrupt Flag Register

$37 ($57)

SPMCR

SPM Control Register

$36 ($56)

TWCR

2-wire Serial Interface Control Register

$35 ($55)

MCUCR

MCU general Control Register

$34 ($54)

MCUSR

MCU general Status Register

$33 ($53)

TCCR0

Timer/Counter0 Control Register

$32 ($52)

TCNT0

Timer/Counter0 (8-bit)

$31 ($51)

OSCCAL

Oscillator Calibration Register

$30 ($50)

SFIOR

Special Function I/O Register

$2F ($4F)

TCCR1A

Timer/Counter1 Control Register A

$2E ($4E)

TCCR1B

Timer/Counter1 Control Register B

$2D ($4D)

TCNT1H

Timer/Counter1 High-byte

$2C ($4C)

TCNT1L

Timer/Counter1 Low-byte

$2B ($4B)

OCR1AH

Timer/Counter1 Output Compare Register A High-byte

$2A ($4A)

OCR1AL

Timer/Counter1 Output Compare Register A Low-byte

$29 ($49)

OCR1BH

Timer/Counter1 Output Compare Register B High-byte

System Clock Ø

WR

RD

Data

Data

Address

Address

T1

T2

T3

T4

Prev. Address

Read

W

rite