Atmega163(l) – Rainbow Electronics ATmega163L User Manual

Page 141

ATmega163(L)

141

Notes:

1. In ATmega163, this parameter is characterized and not 100% tested.

2. Required only for f

SCL

> 100 kHz.

3. C

b

= capacitance of one bus line in pF.

4. f

CK

= CPU clock frequency

5. This requirement applies to all ATmega163 2-wire Serial Interface operation. Other devices connected to the 2-wire Serial

Bus need only obey the general f

SCL

requirement.

6. The actual low period generated by the ATmega163 2-wire Serial Interface is (1/f

SCL

- 2/f

CK

), thus f

CK

must be greater than 6

MHz for the low time requirement to be strictly met at f

SCL

= 100 kHz.

7. The actual low period generated by the ATmega163 2-wire Serial Interface is (1/f

SCL

- 2/f

CK

), thus the low time requirement

will not be strictly met for f

SCL

> 308 kHz when f

CK

= 8 MHz. Still, ATmega163 devices connected to the bus may communi-

cate at full speed (400 kHz) with other ATmega163 devices, as well as any other device with a proper t

LOW

acceptance

margin.

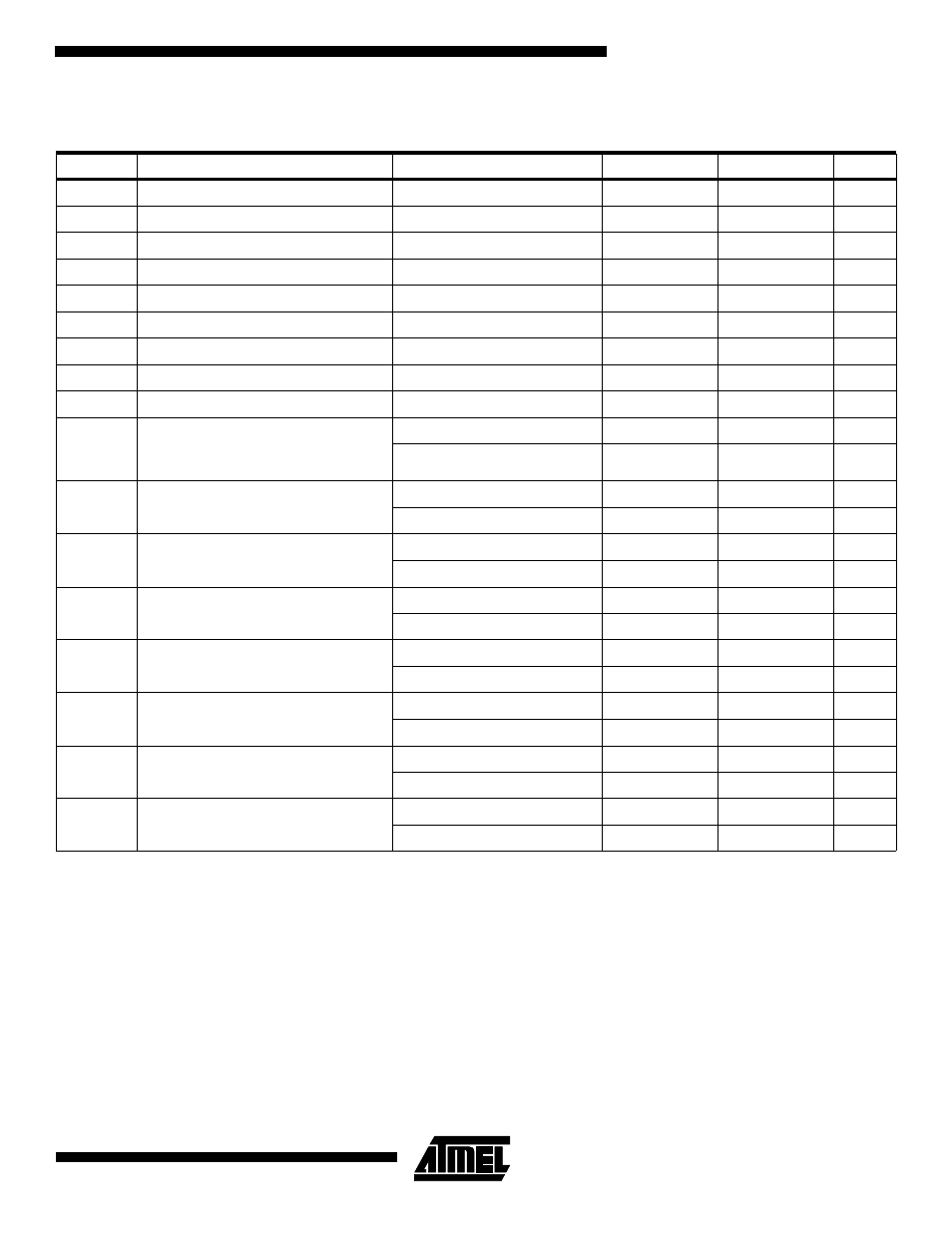

Table 64. 2-wire Serial Bus Requirements

Symbol

Parameter

Condition

Min

Max

Units

V

IL

Input Low-voltage

-0.5

0.3 V

CC

V

V

IH

Input High-voltage

0.7 V

CC

V

CC

+ 0.5

V

V

hys

Hysteresis of Schmitt Trigger Inputs

0.05 V

CC

-

V

V

Output Low-voltage

3 mA sink current

0

0.4

V

t

of

Output Fall Time from V

IHmin

to V

ILmax

10 pF < C

b

< 400 pF

20 + 0.1C

b

250

ns

t

SP

Spikes Suppressed by Input Filter

0

50

ns

I

i

Input Current each I/O Pin

0.1V

CC

< V

i

< 0.9V

CC

-10

10

µA

C

i

Capacitance for each I/O Pin

-

10

pF

f

SCL

SCL Clock Frequency

f

> max(16f

SCL

, 250kHz)

0

400

kHz

t

HD;STA

Hold Time (repeated) START

Condition

f

SCL

≤ 100 kHz

4.0

-

µs

f

SCL

> 100 kHz

0.6

-

µs

t

LOW

Low Period of the SCL Clock

f

SCL

≤ 100 kHz

4.7

-

µs

f

SCL

> 100 kHz

1.3

-

µs

t

HIGH

High period of the SCL clock

f

SCL

≤ 100 kHz

4.0

-

µs

f

SCL

> 100 kHz

0.6

-

µs

t

SU;STA

Set-up time for a repeated START

condition

f

SCL

≤ 100 kHz

4.7

-

µs

f

SCL

> 100 kHz

0.6

-

µs

t

HD;DAT

Data hold time

f

SCL

≤ 100 kHz

0

3.45

µs

f

SCL

> 100 kHz

0

0.9

µs

t

SU;DAT

Data setup time

f

SCL

≤ 100 kHz

250

-

ns

f

SCL

> 100 kHz

100

-

ns

t

SU;STO

Setup time for STOP condition

f

SCL

≤ 100 kHz

4.0

-

µs

f

SCL

> 100 kHz

0.6

-

µs

t

BUF

Bus free time between a STOP and

START condition

f

SCL

≤ 100 kHz

4.7

-

µs

f

SCL

> 100 kHz

1.3

-

µs