Table 1-11. mcecc internal register memory map -35, Table 1-11 – Motorola MVME172 User Manual

Page 53

Memory Maps

http://www.mcg.mot.com/literature

1-35

1

The following MCECC memory map applies only to the 200/300-Series MVME172

boards.

$80

PACER INT

CONTROL

0

IRE

INT

IEN

ICLR

IL2

IL1

IL0

$81

PACER GEN

CONTROL

PLTY

PLS

0

EN

CLR

PS2

PS1

PS0

$82

PACER

TIMER

T15

T14

T13

T12

T11

T10

T9

T8

$83

PACER

TIMER

T7

T6

T5

T4

T3

T2

T1

T0

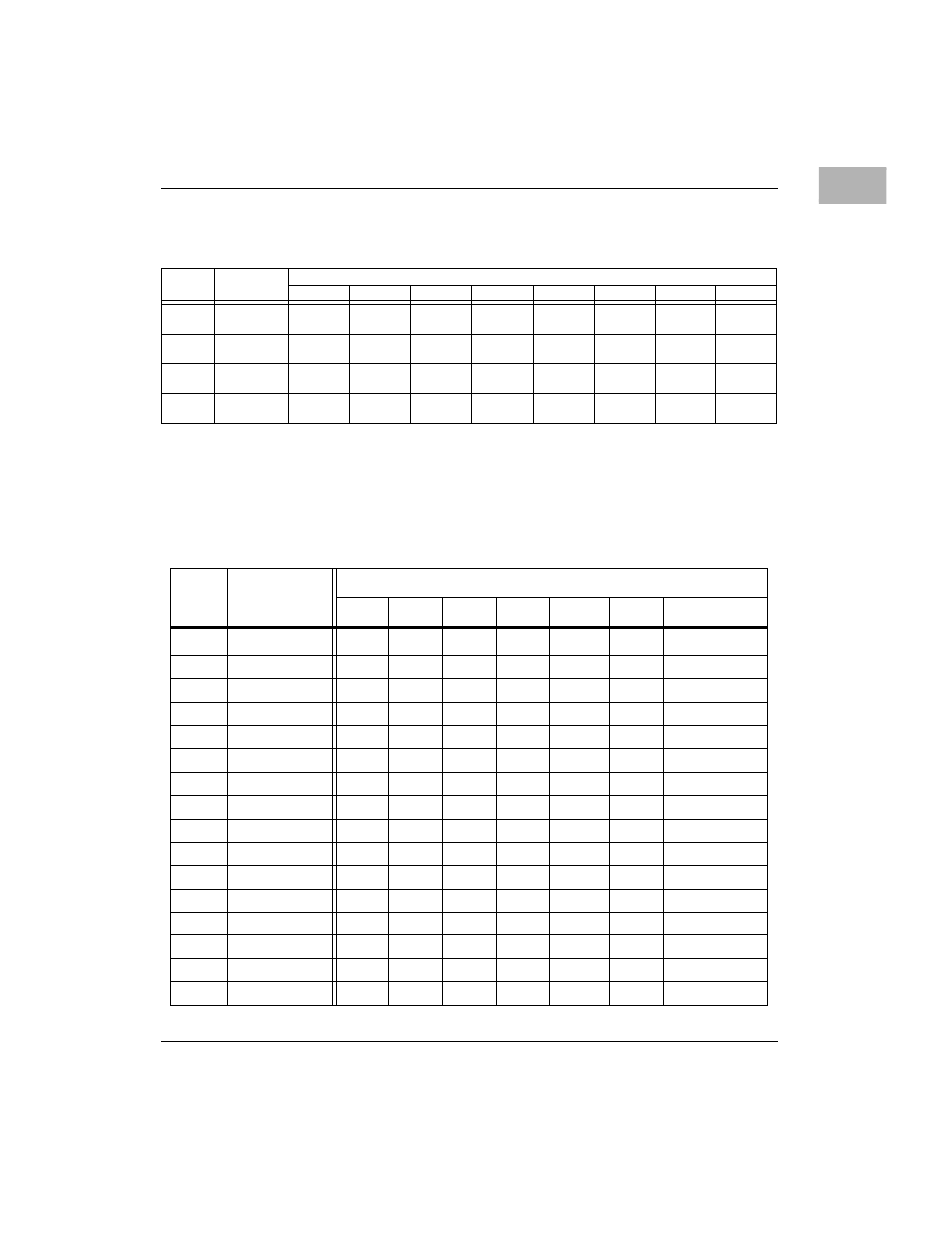

Table 1-11. MCECC Internal Register Memory Map

MCECC Base Address = $FFF43000 (1st); $FFF43100 (2nd)

Register

Offset

Register

Name

Register Bit Names

D31

D30

D29

D28

D27

D26

D25

D24

$00

CHIP ID

CID7

CID6

CID5

CID4

CID3

CID2

CID1

CID0

$04

CHIP REVISION

REV7

REV6

REV5

REV4

REV3

REV2

REV1

REV0

$08

MEM CONFIG

FSTRD

1

0

MSIZ2

MSIZ1

MSIZ0

$0C

DUMMY 0

0

0

0

0

0

0

0

0

$10

DUMMY 1

0

0

0

0

0

0

0

0

$14

BASE ADDRESS

BAD31

BAD30

BAD29

BAD28

BAD27

BAD26

BAD25

BAD24

$18

DRAM CONTRL

BAD23

BAD22

RWB5

SWAIT

RWB3

NCEIEN

NCEBEN

RAMEN

$1C

BCLK FREQ

BCK7

BCK6

BCK5

BCK4

BCK3

BCK2

BCK1

BCK0

$20

DATA CONTRL

0

0

DERC

ZFILL

RWCKB

0

0

0

$24

SCRUB CNTRL

RACODE

RADATA

HITDIS

SCRB

SCRBEN

0

SBEIEN

IDIS

$28

SCRUB PERIOD

SBPD15

SBPD1

4

SBPD1

3

SBPD1

2

SBPD1

1

SBPD1

0

SBPD

9

SBPD

8

$2C

SCRUB PERIOD

SBPD

7

SBPD

6

SBPD

5

SBPD

4

SBPD

3

SBPD

2

SBPD

1

SBPD

0

$30

CHIP PRESCALE

CPS7

CPS6

CPS5

CPS4

CPS3

CPS2

CPS1

CPS0

$34

SCRUB TIME ON/OFF

SRDIS

0

STON2

STON

1

STON

0

STOFF2

STOFF

1

STOFF

0

$38

SCRUB PRESCALE

0

0

SPS21

SPS2

0

SPS

19

SPS

18

SPS

17

SPS

16

$3C

SCRUB PRESCALE

SPS

15

SPS

14

SPS

13

SPS

12

SPS

11

SPS

10

SPS

9

SPS

8

Table 1-10. IP2 Chip Memory Map - Control and Status Registers

(Continued)

Register

Offset

Register

Name

Register Bit Names

D7

D6

D5

D4

D3

D2

D1

D0