General control register, General control register -12, 3general control register – Motorola MVME172 User Manual

Page 200

3-12

Computer Group Literature Center Web Site

MC2 Chip

3

General Control Register

FAST

This control bit tailors the control circuit for BBRAM to

the speed of BBRAM.

When operating at 25 MHz, the FAST bit should be

cleared for devices with access times longer than 200 ns

(5 CLK cycles). The bit can be set for devices that have

access times of 200 ns or faster. It is not allowed to use

devices slower than 360 ns (9 CLK cycles), at 25 MHz.

When operating at 32 MHz, the FAST bit should be

cleared for devices with access times longer than 150 ns

(5 CLK cycles). The bit can be set for devices that have

access times of 150 ns or faster. It is not allowed to use

devices slower than 270 ns (9 CLK cycles), at 32 MHz.

MIEN

Master Interrupt Enable. When this bit is high, interrupts

from and via the MC2 chip are allowed to reach the MPU.

When it is low, all interrupts from the MC2 chip are

disabled. Also, when the bit is low, all interrupt

acknowledge cycles to the MC2 chip are passed on, via

the IACKOUT* pin. This bit is cleared by a reset.

PPC

PowerPC interrupt mode. When this bit is high, the

IPL<2> signal output is compatible with the int signal on

the PowerPC. When this bit is low, the IPL signal outputs

are compatible with the MC68060.

!

Caution

This bit is low for the MVME172 boards. Do not change it. If

it is changed, the board will not operate properly.

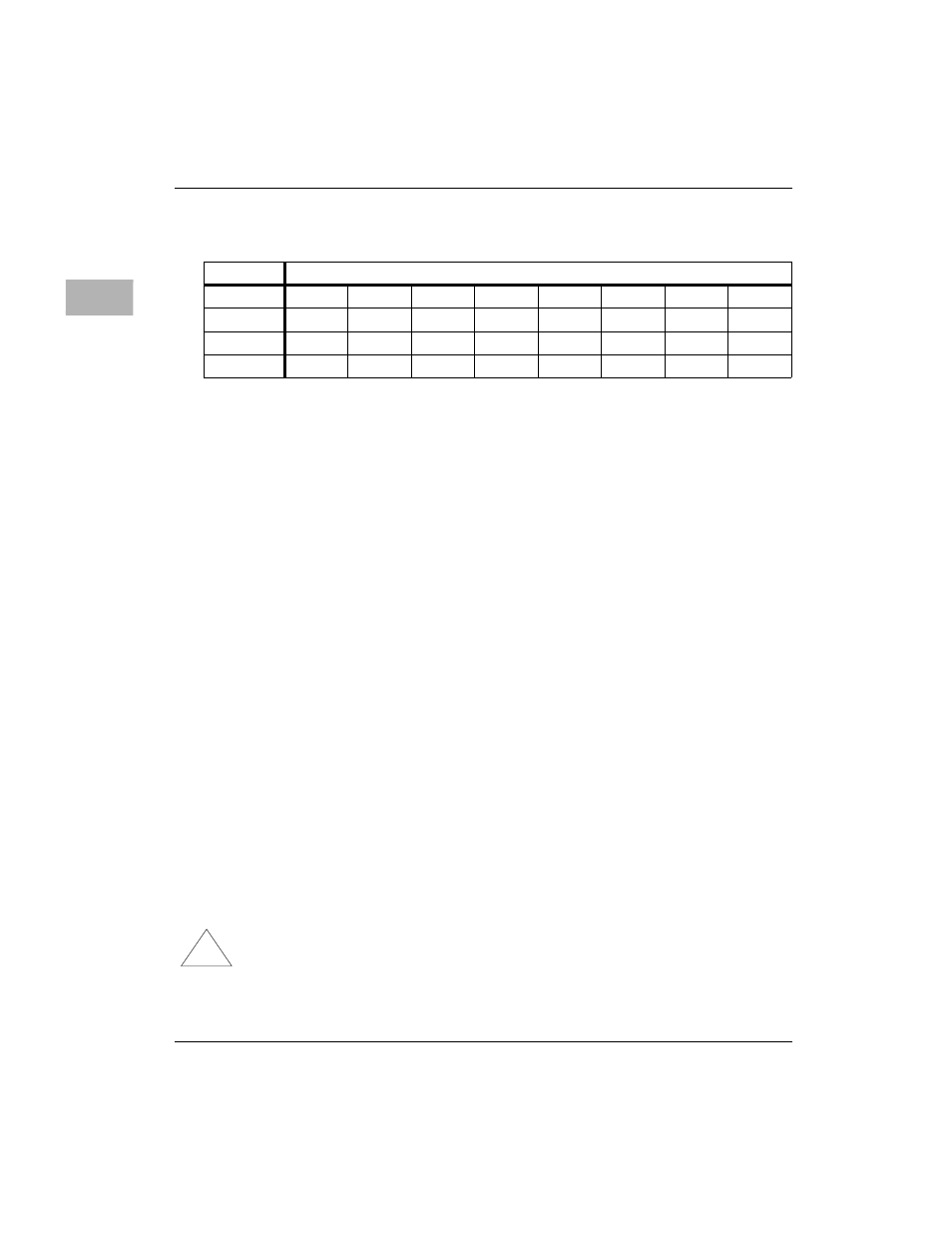

ADR/SIZ

$FFF42000 (8 bits)

BIT

15

14

13

12

11

10

9

8

NAME

SCCIT1 SCCIT0

PPC

MIEN

FAST

OPER

R

R

R

R/W

R/W

R/W

R/W

R/W

RESET

0 PL

0 PL

0 PL

0 PL

0 PL

0 PL

0 PL

0 P