Motorola MVME172 User Manual

Page 252

4-16

Computer Group Literature Center Web Site

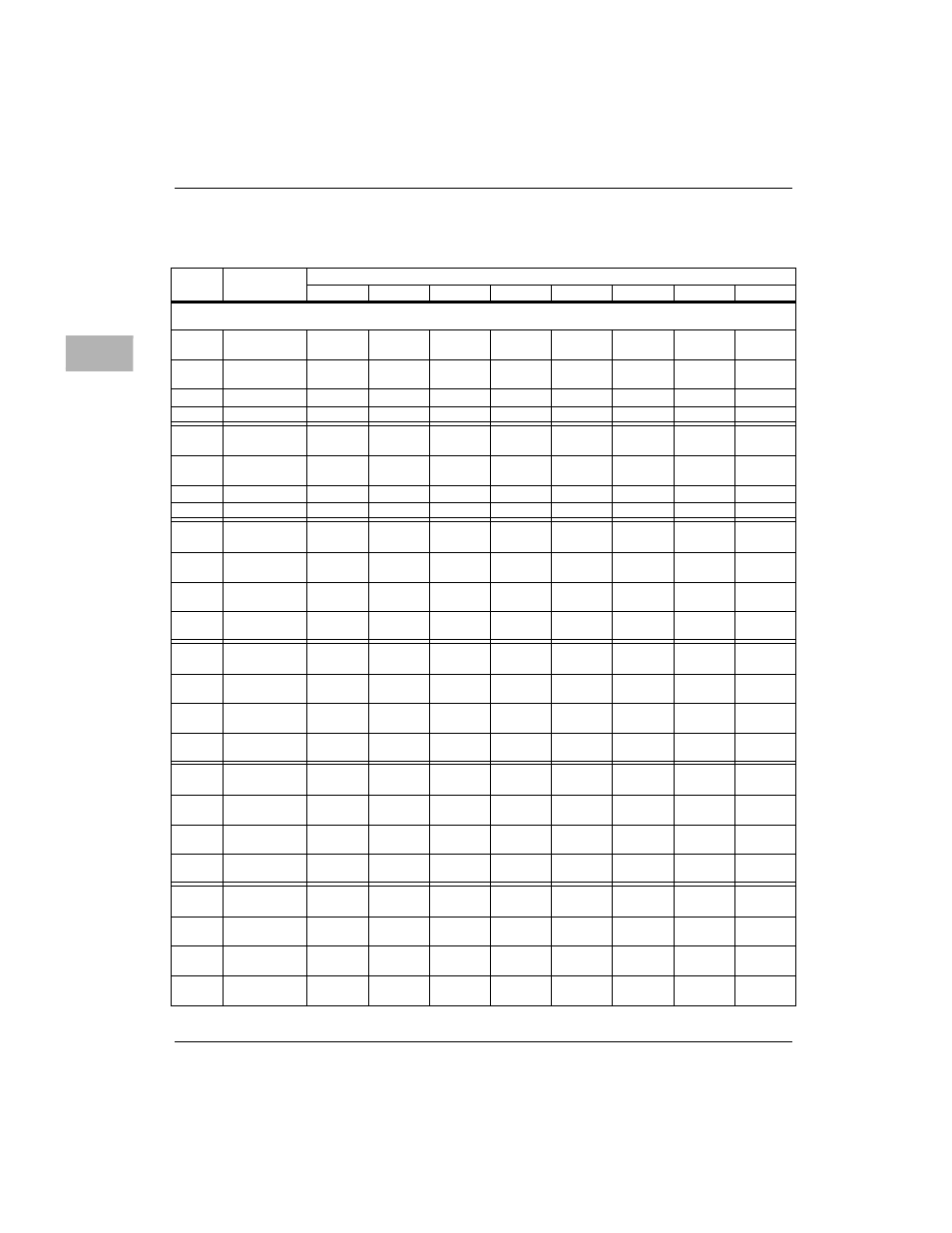

IP2 Chip

4

DMAC for IndustryPack d, request 0 or for IndustryPack c, request 1, and for programmable CLOCK.

This register set, not including the programmable Clock, is referred to as DMACd in the text.

$68

DMA_d

STATUS

0

DLBE

0

IPEND

CHANI

TBL

IPTO

DONE

$69

DMA_d INT

CTRL

0

0

DINT

DIEN

DICLR

DIL2

DIL1

DIL0

$6a

DMA ENABLE

0

0

0

0

0

0

0

DEN

$6b

RESERVED

0

0

0

0

0

0

0

0

$6c

DMA_d CON-

TROL 1

DHALT

0

DTBL

ADMA

WIDTH1

WIDTH0

C_CH1

XXX

$6d

DMA_d CON-

TROL 2

INTE

0

DMAEI

DMAEO

ENTO

TOIP

0

0

$6e

RESERVED

0

0

0

0

0

0

0

0

$6f

RESERVED

0

0

0

0

0

0

0

0

$70

DMA_d LB

ADDR

LBA31

LBA30

LBA29

LBA28

LBA27

LBA26

LBA25

LBA24

$71

DMA_d LB

ADDR

LBA23

LBA22

LBA21

LBA20

LBA19

LBA18

LBA17

LBA16

$72

DMA_d LB

ADDR

LBA15

LBA14

LBA13

LBA12

LBA11

LBA10

LBA9

LBA8

$73

DMA_d LB

ADDR

LBA7

LBA6

LBA5

LBA4

LBA3

LBA2

LBA1

LBA0

$74

DMA_d IP

ADDR

0

0

0

0

0

0

0

0

$75

DMA_d IP

ADDR

IPA23

IPA22

IPA21

IPA20

IPA19

IPA18

IPA17

IPA16

$76

DMA_d IP

ADDR

IPA15

IPA14

IPA13

IPA12

IPA11

IPA10

IPA9

IPA8

$77

DMA_d IP

ADDR

IPA7

IPA6

IPA5

IPA4

IPA3

IPA2

IPA1

IPA0

$78

DMA_d BYTE

CNT

0

0

0

0

0

0

0

0

$79

DMA_d BYTE

CNT

BCNT23

BCNT22

BCNT21

BCNT20

BCNT19

BCNT18

BCNT17

BCNT16

$7a

DMA_d BYTE

CNT

BCNT15

BCNT14

BCNT13

BCNT12

BCNT11

BCNT10

BCNT9

BCN8

$7b

DMA_d BYTE

CNT

BCNT7

BCNT6

BCNT5

BCNT4

BCNT3

BCNT2

BCNT1

BCNT0

$7c

DMA_d TBL

ADDR

TA31

TA30

TA29

TA28

TA27

TA26

TA25

TA24

$7d

DMA_d TBL

ADDR

TA23

TA22

TA21

TA20

TA19

TA18

TA17

TA16

$7e

DMA_d TBL

ADDR

TA15

TA14

TA13

TA12

TA11

TA10

TA9

TA8

$7f

DMA_d TBL

ADDR

TA7

TA6

TA5

TA4

TA3

TA2

TA1

TA0

Table 4-3. IP2 Chip Memory Map - Control and Status Registers (Continued)

IP2 Chip Base Address = $FFFBC000

Register

Offset

Register Name

Register Bit Names

D7

D6

D5

D4

D3

D2

D1

D0