Table 1-1. mvme172 features summary -3 – Motorola MVME172 User Manual

Page 21

Overview

http://www.mcg.mot.com/literature

1-3

1

The MCECC chip Memory Controller ASIC on the 200/300-Series

MVME172 provides the programmable interface for the ECC-protected

16 MB DRAM mezzanine board.

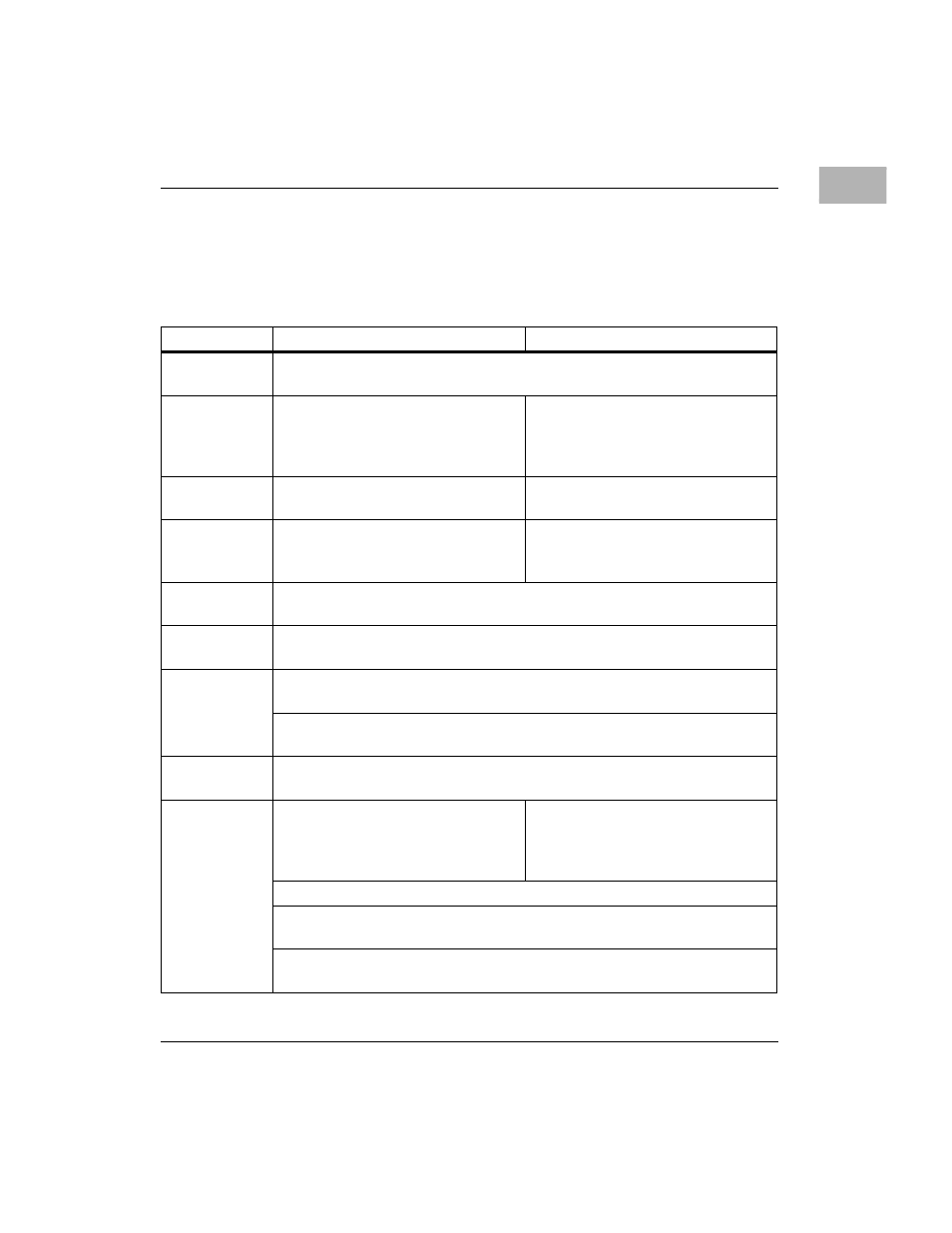

Table 1-1. MVME172 Features Summary

Feature

200/300-Series

400/500-Series

Processor

6

0 MHz 32-bit MC68060 microprocessor, or 64 MHz 32-bit

MC68LC060 microprocessor

DRAM

4MB, 8 MB, or 16 MB of shared

DRAM with parity protection on a

mezzanine module, or up to 64 MB of

ECC-protected DRAM

4MB, 8 MB, or 16 MB of shared

DRAM with no protection

SRAM

128 K

B of SRAM with battery

backup

512KB of SRAM with battery backup

PROM/

EPROM

Sockets

Two JEDEC standard 32-pin DIP

PROM sockets

O

ne JEDEC standard 32-pin

PLCC EPROM socket (EPROMs

may

be shipped separatel

y)

Flash

One Inte

l 28F016SA 2M x 8 Flash memory device (2MB Flash

memory

total) with write protection (optional)

NVRAM and

TOD

8K by 8 Non-Volatile RAM (NVRAM) and Time-of-Day (TOD) clock with

battery backup

Timers

Four 32-bit Tick Timers and Watchdog Timer (in the MC2 Chip ASIC) for

periodic interrupts

Two 32-bit Tick Timers and Watchdog Timer in the VMEchip2 ASIC) for

periodic interrupts

Software

Interrupts

Eight software interrupts (for MVME172 versions that have the VMEchip2)

I/O

Four serial ports, both EIA-232-D RJ-

45

Tw

o serial ports; one EIA-232-D

DCE, one EIA-232-D DCE/DTE or

EIA-530 DCE/DTE or EIA-42

DCE/DTE or EIA-485

Serial port controller

s (Zilog Z85230)

Optional Small Computer Systems Interface (SCSI) bus interface with 32-bit

local bus burst Direct Memory Access (DMA) (NCR 53C710 controller)

Optional LAN Ethernet transceiver interface with 32-bit local bus DMA (Inter

82596CA controller)