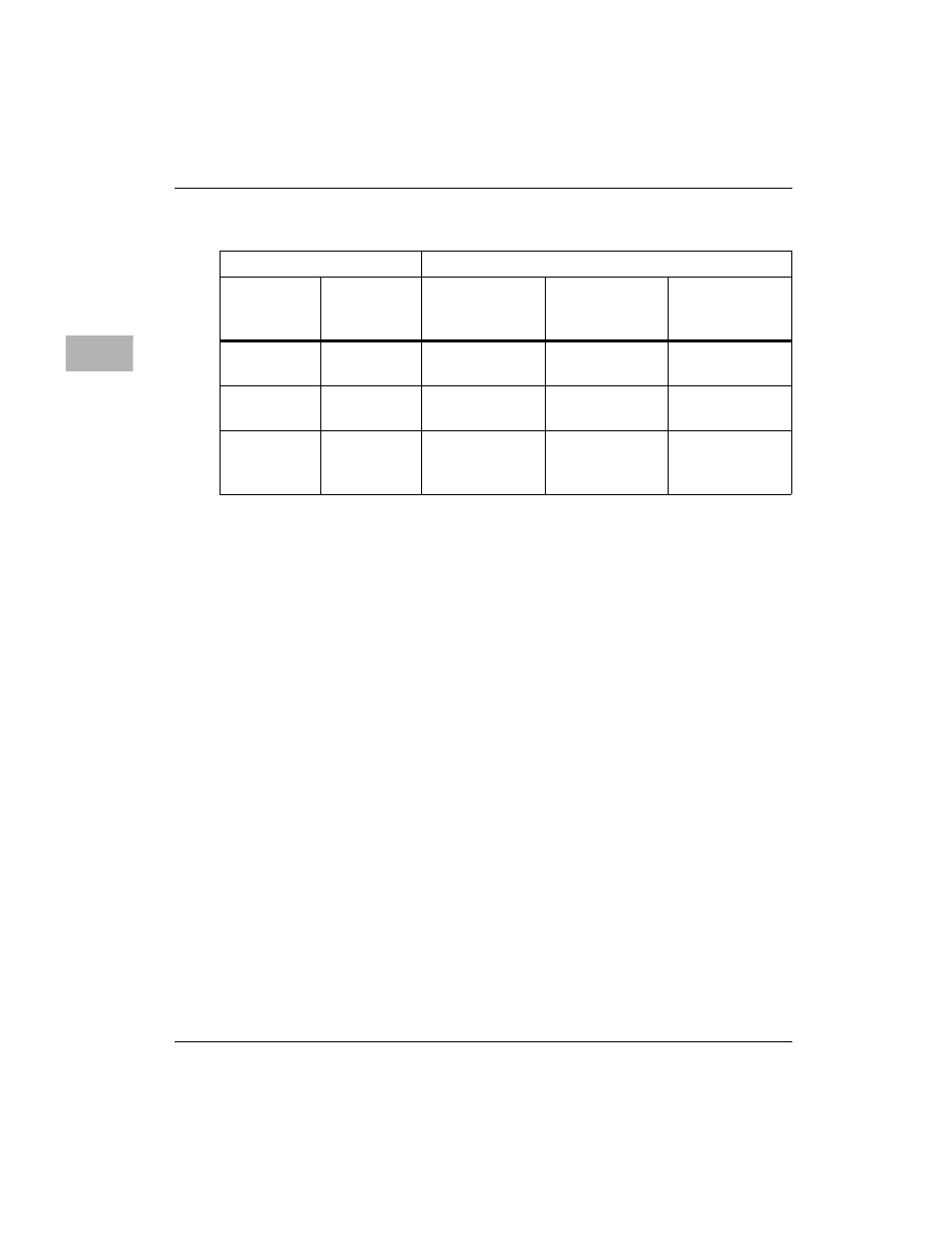

Table 4-1. ip2 chip clock cycles -6 – Motorola MVME172 User Manual

Page 242

4-6

Computer Group Literature Center Web Site

IP2 Chip

4

Notes

1. This column is a measure of IndustryPack bandwidth for

back to back cycles for a local bus master which is accessing

a memory or I/O space location on an IndustryPack. It

assumes a zero wait state acknowledge reply from the

IndustryPack.

2. This column is a measure of IndustryPack bandwidth for

DMA burst cycles between a local bus slave and a memory

or I/O space location on an IndustryPack. It assumes a zero

wait state acknowledge reply from the IndustryPack.

3. This column is a measure of IndustryPack bandwidth for

DMA single cycles between a local bus slave and a memory

or I/O space location on an IndustryPack. It assumes a zero

wait state acknowledge reply from the IndustryPack.

4. Burst mode sDMA is not supported when both bus

frequencies are 32 MHz.

5. Because the specified band width assumes a zero wait state

IndustryPack cycle, it would be difficult to achieve the stated

bandwidths for an IP bus frequency of 32 MHz.

Table 4-1. IP2 Chip Clock Cycles

Bus Frequency

Period and Bandwidth to 32-Bit IP Space

MC68060

IP

Back to Back

Examine

(Note 1)

Four Cycle

DMA Burst

(Note 2)

Single Cycle

DMA

(Note 3)

25 MHz

8 MHz

4 IP clocks

8 MB/sec

10 IP clocks

12.8 MB/sec

4 IP clocks

8 MB/sec

32 MHz

8 MHz

3 IP clocks

10.6 MB/sec

10 IP clocks

12.8 MB/sec

4 IP clocks

8 MB/sec

32 MHz

32 MHz

(Note 5)

6 IP clocks

21 MB/sec

12 IP clocks

42 MB/sec

(Note 4)

6 IP clocks

21 MB/sec