Table 1-9. ip2 chip overall memory map -28, Table 1-9 – Motorola MVME172 User Manual

Page 46

1-28

Computer Group Literature Center Web Site

Board Description and Memory Maps

1

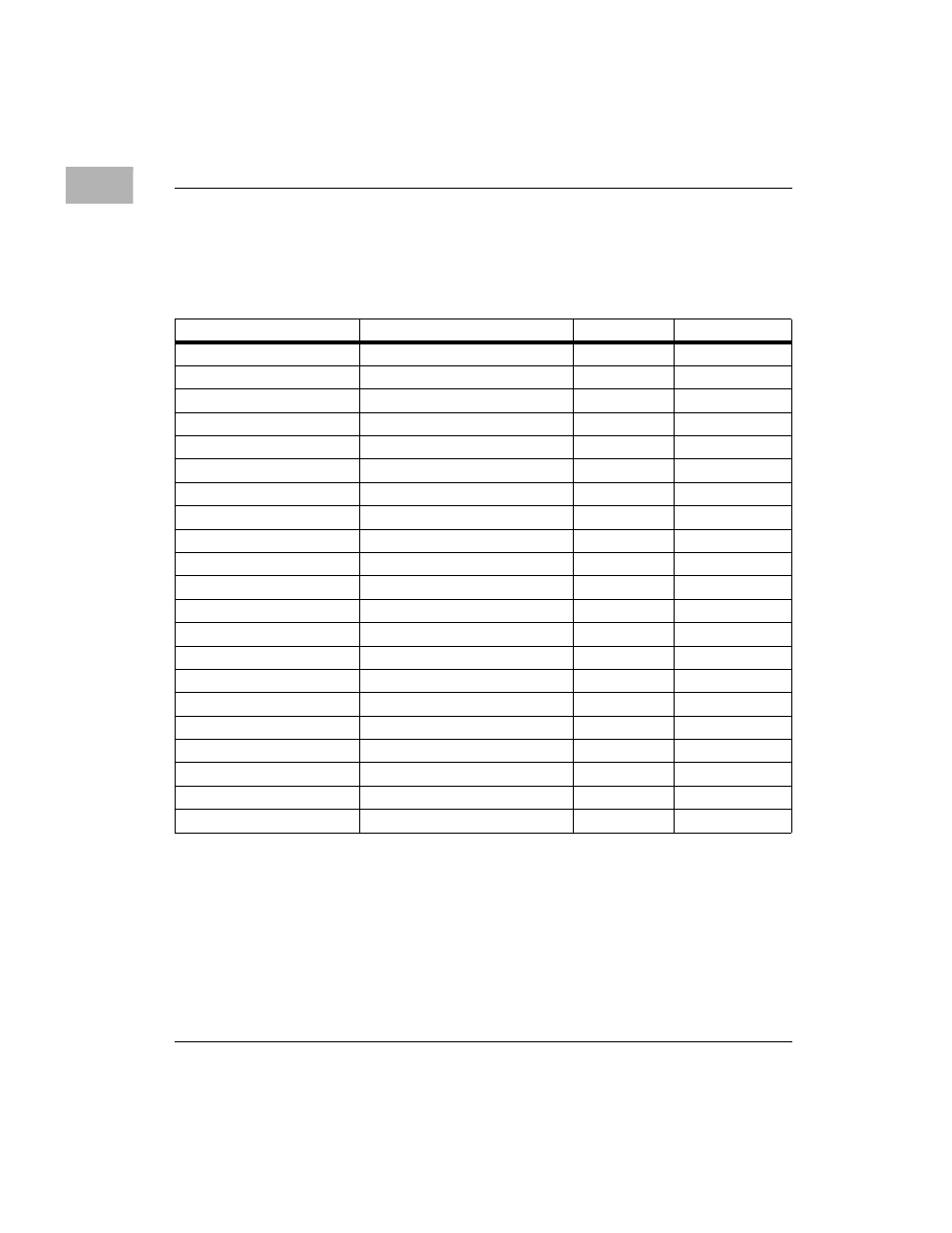

The following memory map table includes all devices selected by the IP2

chip map decoder.

A summary of the IP2 chip CSR registers is shown in

. The CSR

registers can be accessed as bytes, words, or longwords. They should not

be accessed as lines. They are shown in the table as bytes.

Table 1-9. IP2 Chip Overall Memory Map

Address Range

Selected Device

Port Width

Size

Programmable

IP_a/IP_ab Memory Space

D32-D8

64KB-16MB

Programmable

IP_b Memory Space

D16-D8

64KB-8MB

Programmable

IP_c/IP_cd Memory Space

D32-D8

64KB-16MB

Programmable

IP_d Memory Space

D16-D8

64KB-8MB

$FFF58000-$FFF5807F

IP_a I/O Space

D16

128B

$FFF58080-$FFF580BF

IP_a ID Space

D16

64B

$FFF580C0-$FFF580FF

IP_a ID Space Repeated

D16

64B

$FFF58100-$FFF5817F

IP_b I/O Space

D16

128B

$FFF58180-$FFF581BF

IP_b ID Space

D16

64B

$FFF581C0-$FFF581FF

IP_b ID Space Repeated

D16

64B

$FFF58200-$FFF5827F

IP_c I/O Space

D16

128B

$FFF58280-$FFF582BF

IP_c ID Space

D16

64B

$FFF582C0-$FFF582FF

IP_c ID Space Repeated

D16

64B

$FFF58300-$FFF5837F

IP_d I/O Space

D16

128B

$FFF58380-$FFF583BF

IP_d ID Space

D16

64B

$FFF583C0-$FFF583FF

IP_d ID Space Repeated

D16

64B

$FFF58400-$FFF584FF

IP_ab I/O Space

D32-D16

256B

$FFF58500-$FFF585FF

IP_cd I/O Space

D32-D16

256B

$FFF58600-$FFF586FF

IP_ab I/O Space Repeated

D32-D16

256B

$FFF58700-$FFF587FF

IP_cd I/O Space Repeated

D32-D16

256B

$FFFBC000-$FFFBC083

Control/Status Registers

D32-D8

32B