2 configuration registers, Table 9-2, I/o address: 0x0cf8 accessed as a dword – Artesyn ATCA-7350 Installation and Use (September 2014) User Manual

Page 169: Table 9-3, Configuration address register bit assignments, Addressing

Addressing

ATCA-7350 Installation and Use (6806800G59G)

169

9.2

Configuration Registers

9.2.1

Configuration Address Register MCH CONFIG_ADDRESS

Default Value: 0x00000000

Access: Read/Write

Size: 32 bits

CONFIG_ADDRESS is a 32-bit I/O register that can only be accessed as a Dword. A byte or word

reference passes through the Configuration Address Register and hub link interface HI_A onto

the PCI_A bus as an I/O cycle. The CONFIG_ADDRESS register contains the Bus Number, Device

Number, Function Number, and Register Number for which a subsequent PCI configuration

access is intended. This register is defined by the PCI Bus specification.

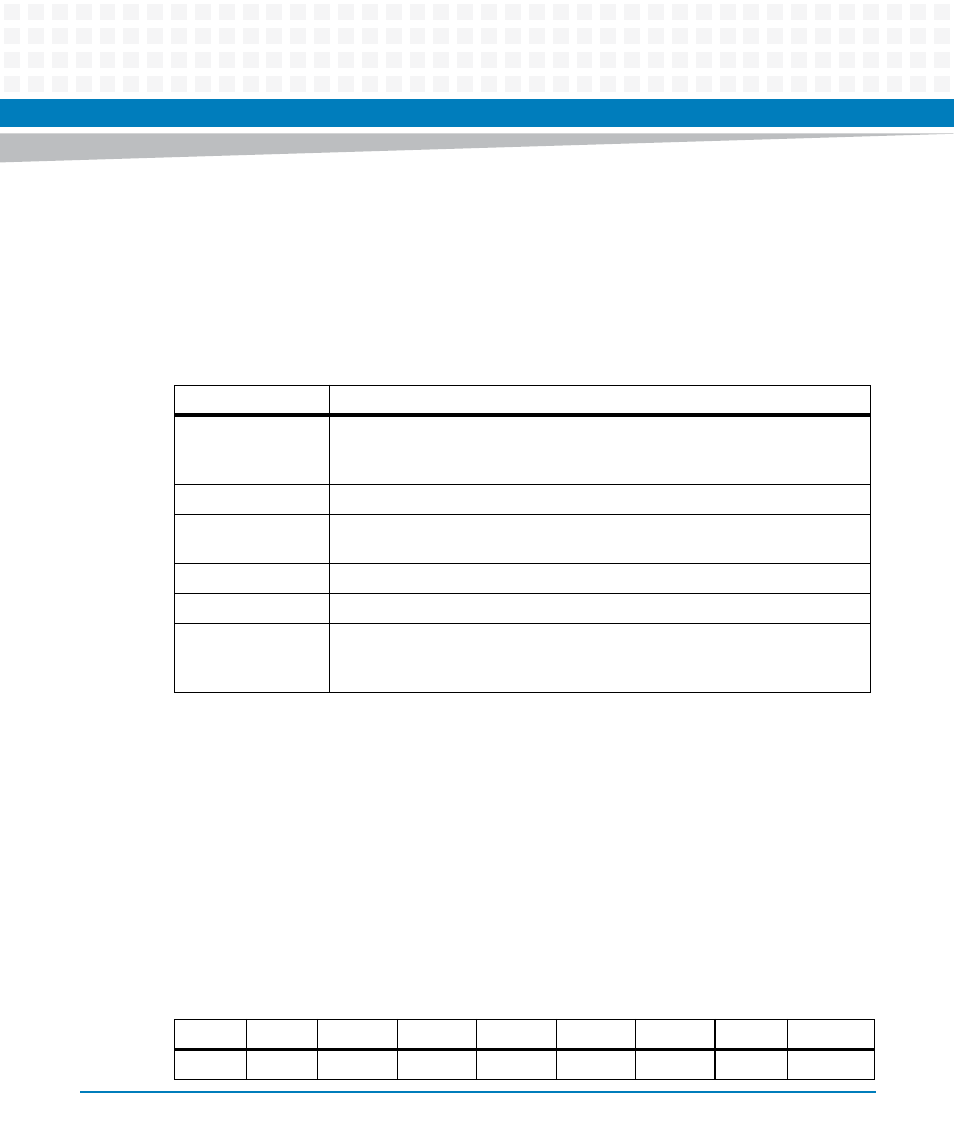

Table 9-2 I/O Address: 0x0CF8 Accessed as a Dword

Bit

Description

31

Configuration Enable (CFGE): When this bit is set to 1, accesses to PCI

configuration space are enabled. When this bit is reset to 0, accesses to PCI

configuration space are disabled.

30:24

Reserved (These bits are read only and have a value of 0).

23:16

Bus Number: Contains the bus number being targeted by the configuration

cycle.

15:11

Device Number: Selects one of the 32 possible devices per bus.

10:8

Function Number: Selects one of eight possible functions within a device.

7:2

Register Number: This field selects one register within a particular Bus, Device,

and Function as specified by the other fields in the Configuration Address

Register. This field is mapped to A[7:2] during HI_A-D Configuration cycles.

Table 9-3 Configuration address register bit assignments

Bit

31

30 24

23 16

15 11

10 8

7 2

1 0

0

R

0

0

0

0

R

Default