Pipe interface signals – Altera Arria V Avalon-ST User Manual

Page 91

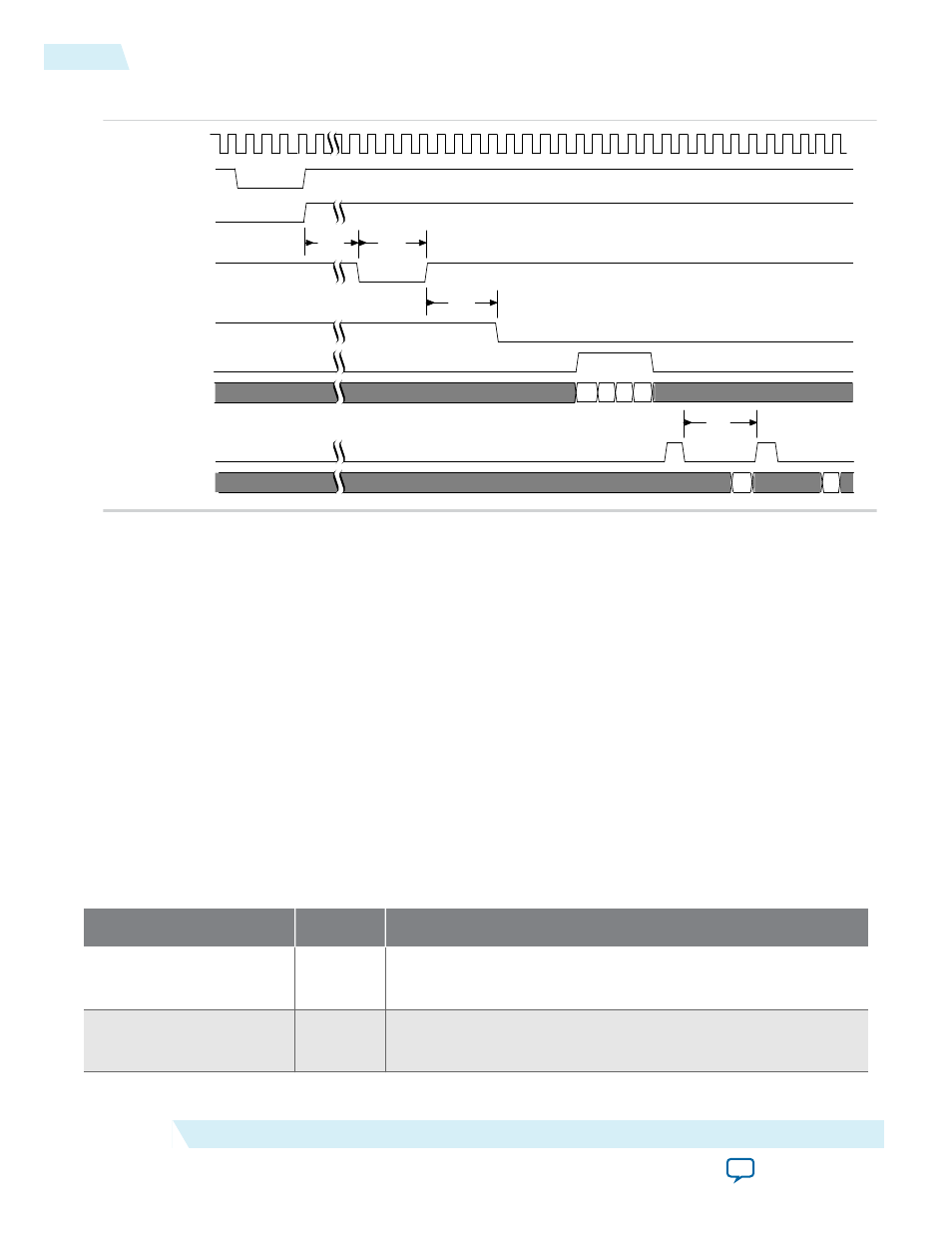

Figure 4-38: Hard IP Reconfiguration Bus Timing of Read-Only Registers

avmm_clk

hip_reconfig_rst_n

user_mode

ser_shift_load

interface_sel

avmm_wr

avmm_wrdata[15:0]

avmm_rd

avmm_rdata[15:0]

D0

D0

D1

D1

D2 D3

324 ns

4 clks

4 clks

4 clks

For a detailed description of the Avalon-MM protocol, refer to the Avalon Memory Mapped Interfaces

chapter in the Avalon Interface Specifications.

Related Information

•

•

PIPE Interface Signals

These PIPE signals are available for Gen1 and Gen2 variants so that you can simulate using either the

serial or the PIPE interface. Simulation is much faster using the PIPE interface because the PIPE

simulation bypasses the SERDES model . By default, the PIPE interface is 8 bits for Gen1 and Gen2. You

can use the PIPE interface for simulation even though your actual design includes a serial interface to the

internal transceivers. However, it is not possible to use the Hard IP PIPE interface in hardware, including

probing these signals using SignalTap

®

II Embedded Logic Analyzer.

Table 4-24: PIPE Interface Signals

In the following table, signals that include lane number 0 also exist for other lanes.

Signal

Direction

Description

txdata0[7:0]

Output

Transmit data

data on lane

txdatak0

Output

Transmit data control

for

txdata

4-54

PIPE Interface Signals

2014.12.15

Altera Corporation

Interfaces and Signal Descriptions