Setting up simulation, Changing between serial and pipe simulation – Altera Arria V Avalon-ST User Manual

Page 232

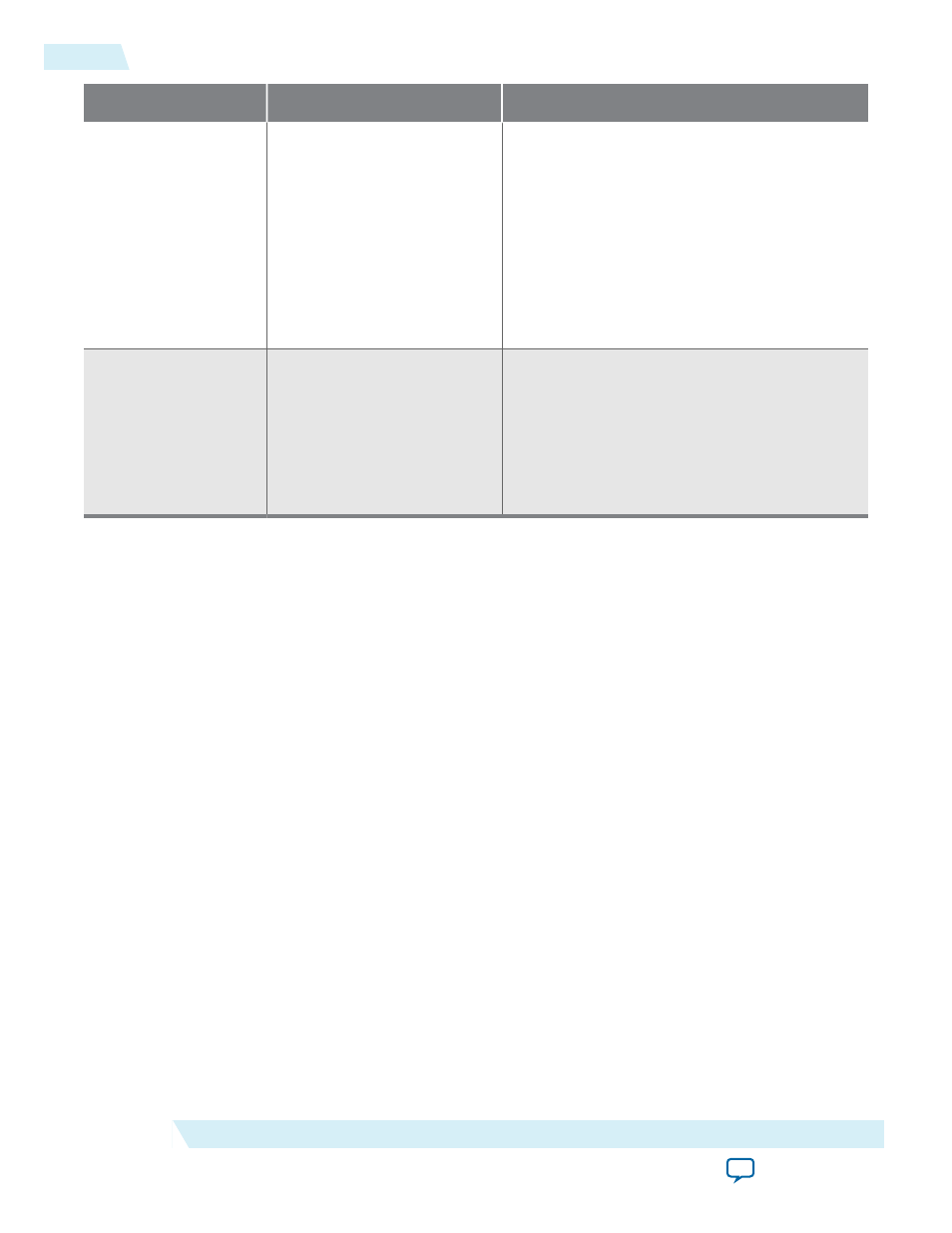

Possible Causes

Symptoms and Root Causes

Workarounds and Solutions

Insufficient Posted

credits released by

Root Port

If a Memory Write TLP is

transmitted with a payload

greater than the maximum

payload size, the Root Port may

release an incorrect posted data

credit to the Endpoint in

simulation. As a result, the

Endpoint does not have enough

credits to send additional

Memory Write Requests.

Make sure Application Layer sends Memory

Write Requests with a payload less than or equal

the value specified by the maximum payload

size.

Missing completion

packets or dropped

packets

The RX Completion TLP might

cause the RX FIFO to overflow.

Make sure that the total

outstanding read data of all

pending Memory Read Requests

is smaller than the allocated

completion credits in RX buffer.

You must ensure that the data for all

outstanding read requests does not exceed the

completion credits in the RX buffer.

Related Information

•

•

•

•

Setting Up Simulation

Changing the simulation parameters reduces simulation time and provides greater visibility.

Changing Between Serial and PIPE Simulation

By default, the Altera testbench runs a serial simulation. You can change between serial and PIPE

simulation by editing the top-level testbench file.

The

hip_ctrl_simu_mode_pipe

signal and

enable_pipe32_sim_hwtcl

parameter, specify serial or PIPE

simulation. When both are set to 1'b0, the simulation runs in serial mode. When both are set to 1'b1, the

simulation runs in PIPE mode. Complete the following steps to enable PIPE simulation. These steps

assume that the actual testbench in Gen1 x4 with an Avalon-MM 64-bit interface.

1. In the top-level testbench, which is

tb.v

, change the signal,

hip_ctrl_simu_mode_pipe

to 1'b1 as shown:

pcie_de_gen1_x4_ast64 pcie_de_gen1_x4_ast64_x_inst (.dut_hip_ctrl_simu_mode_pipe

( 1'b1 ),

2. In the top-level HDL module for the Hard IP which is

simulation/submodules/

change the parameter

enable_pipe32_sim_hwtcl

parameter to 1'b1

as shown:

17-4

Setting Up Simulation

2014.12.15

Altera Corporation

Debugging