Altera Arria V Avalon-ST User Manual

Page 198

Offset (Bytes)

Description

+60

Reserved

The configuration routine does not configure any advanced PCI Express capabilities such as the AER

capability.

Besides the

ebfm_cfg_rp_ep

procedure in altpcietb_bfm_driver_rp.v, routines to read and write

Endpoint Configuration Space registers directly are available in the Verilog HDL include file. After the

ebfm_cfg_rp_ep

procedure is run the PCI Express I/O and Memory Spaces have the layout as described

in the following three figures. The memory space layout is dependent on the value of the add

r_map_4GB_limit input parameter. If addr_map_4GB_limit is 1 the resulting memory space map is

shown in the following figure.

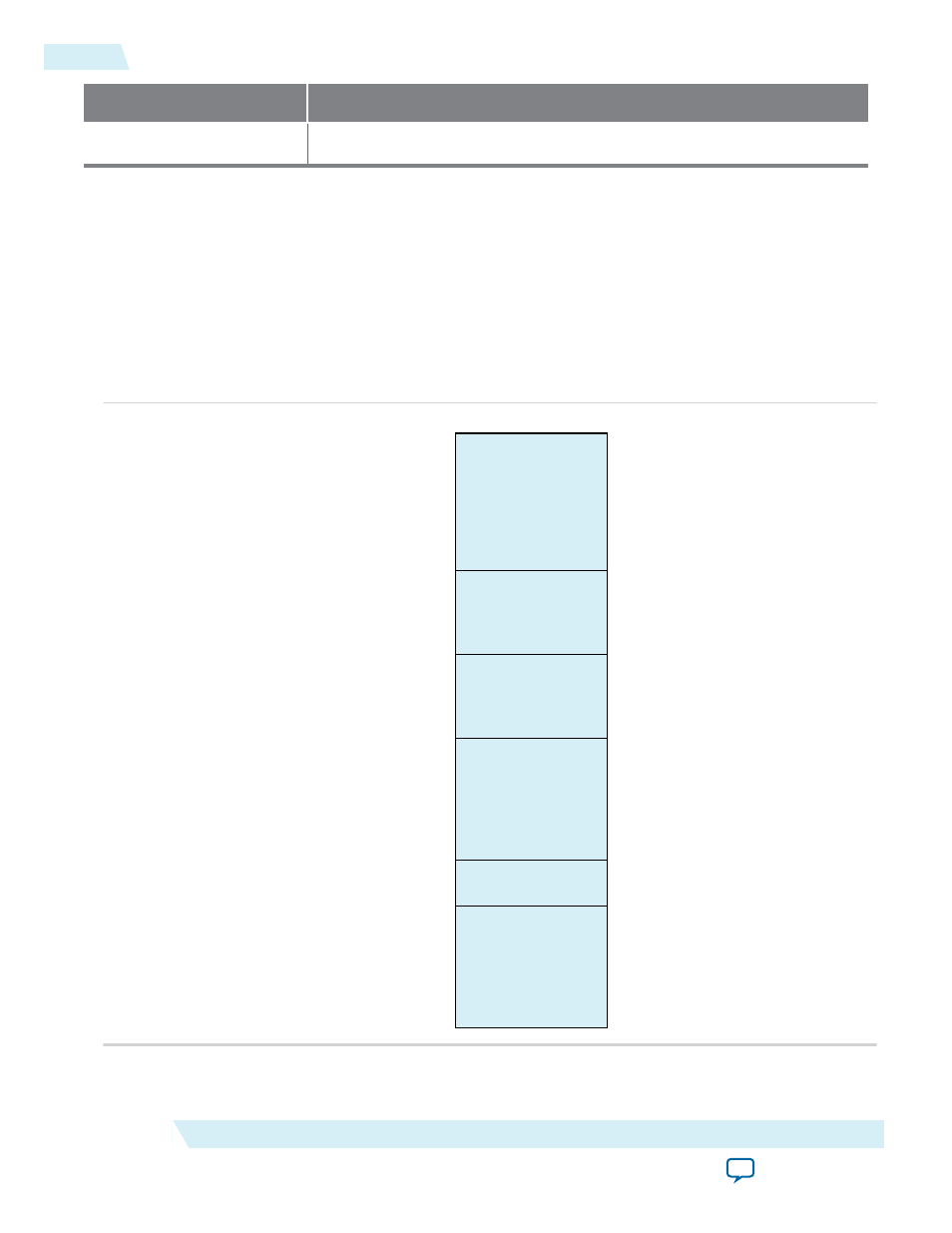

Figure 16-5: Memory Space Layout—4 GByte Limit

Root Complex

Shared Memory

Unused

Configuration Scratch

Space Used by

BFM Routines - Not

Writeable by User

Calls or Endpoint

BAR Table

Used by BFM

Routines - Not

Writeable by User

Calls or End Point

Endpoint Non-

Prefetchable Memory

Space BARs

Assigned Smallest

to Largest

Endpoint Memory

Space BARs

Prefetchable 32-bit

and 64-bit

Assigned Smallest

to Largest

0xFFFF FFFF

0x0020 0000

0x0000 0000

Address

0x001F FFC0

0x001F FF80

If addr_map_4GB_limit is 0, the resulting memory space map is shown in the following figure.

16-28

Configuration of Root Port and Endpoint

2014.12.15

Altera Corporation

Testbench and Design Example