Configuration space register access timing – Altera Arria V Avalon-ST User Manual

Page 74

tl_cfg_sts

Configuration Space Register

Description

[30]

Link Status 2 Reg[0]

Current de-emphasis level.

[29:25]

Status Reg[15:11]

Records the following 5 primary command

status errors:

• Bit 15: detected parity error

• Bit 14: signaled system error

• Bit 13: received master abort

• Bit 12: received target abort

• Bit 11: signalled target abort

[24]

Secondary Status Reg[8]

Master data parity error

[23:6]

Root Status Reg[17:0]

Records the following PME status information:

• Bit 17: PME pending

• Bit 16: PME status

• Bits[15:0]: PME request ID[15:0]

[5:1]

Secondary Status Reg[15:11] Records the following 5 secondary command

status errors:

• Bit 15: detected parity error

• Bit 14: received system error

• Bit 13: received master abort

• Bit 12: received target abort

• Bit 11: signalled target abort

[0]

Secondary Status Reg[8]

Master Data Parity Error

Configuration Space Register Access Timing

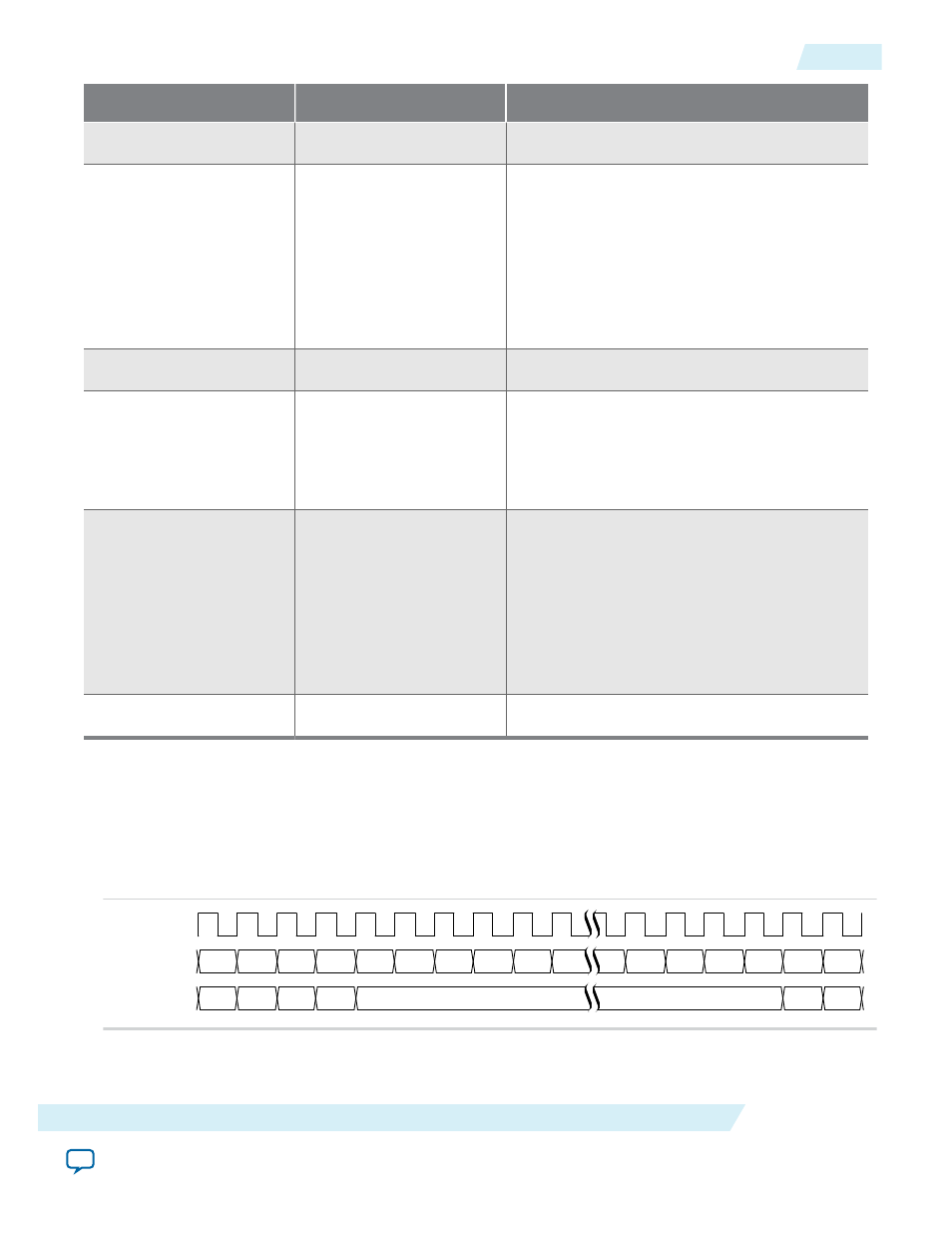

Figure 4-27: tl_cfg_ctl Timing

The following figure shows typical traffic on the

tl_cfg_ctl

bus. The

tl_cfg_add

index increments on

the rising edge of the

pld_clk

. The address specifies which Configuration Space register data value is

being driven onto

tl_cfg_ctl

.

pld_clk

tl_cfg_add[3:0]

tl_cfg_ctl[31:0]

2

3

4

5

6

7

8

9

A

B

8

9

A

B

C

D

E

00... 00... 00... 7F...

00000000

00000000

00... 00...

2014.12.15

Configuration Space Register Access Timing

4-37

Interfaces and Signal Descriptions

Altera Corporation