Altera Arria V Avalon-ST User Manual

Page 76

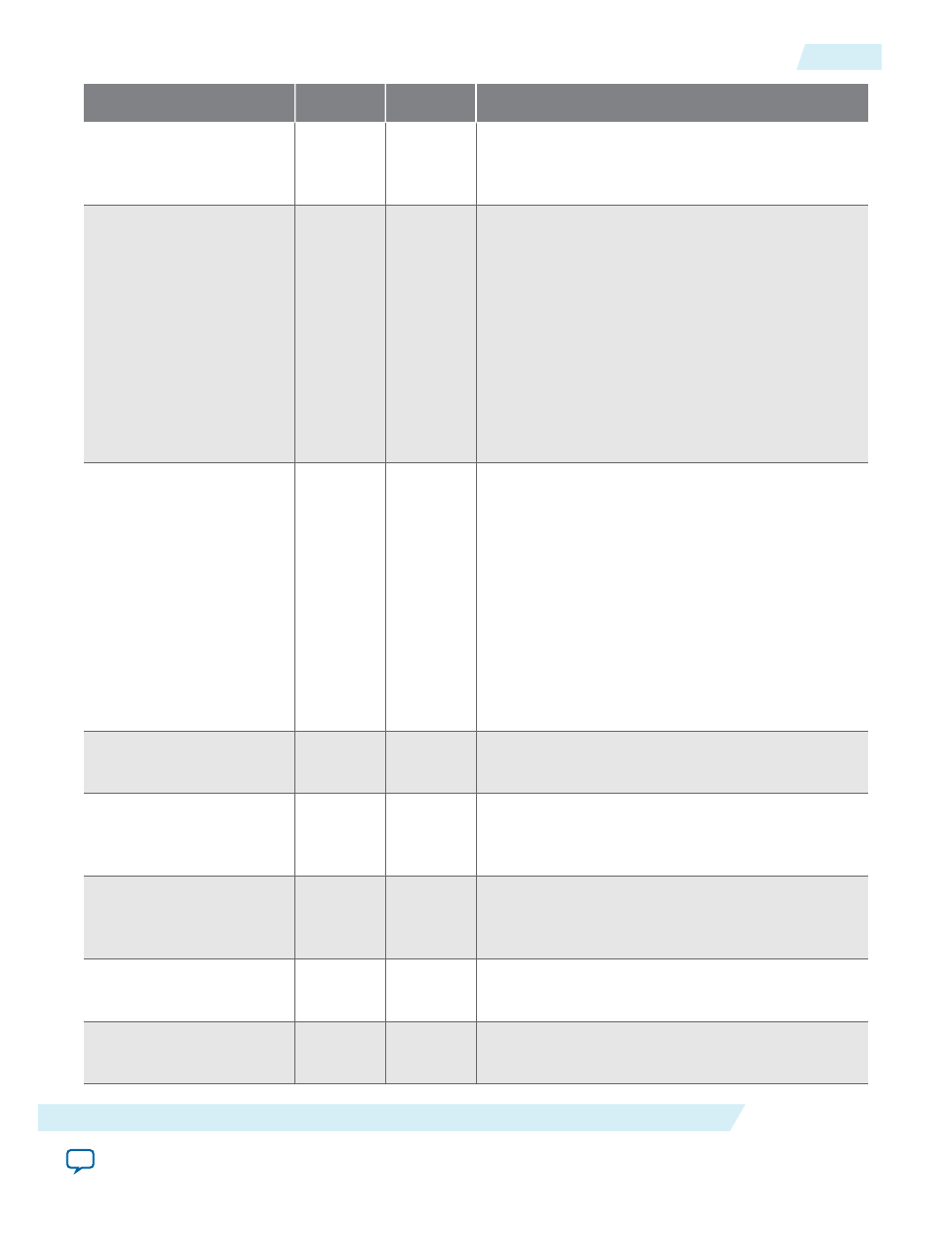

Register

Width

Direction

Description

cfg_slot_ctrl

16

Output

cfg_slot_ctrl[15:0]

is the Slot Status of the PCI

Express capability structure. This register is only

available in Root Port mode.

cfg_link_ctrl

16

Output

cfg_link_ctrl[15:0]

is the primary Link Control

of the PCI Express capability structure.

For Gen2 operation, you must write a 1’b1 to the

Retrain Link bit (Bit[5] of the

cfg_link_ctrl)

of

the Root Port to initiate retraining to a higher data

rate after the initial link training to Gen1 L0 state.

Retraining directs the LTSSM to the Recovery state.

Retraining to a higher data rate is not automatic for

the Arria V Hard IP for PCI Express IP Core even if

both devices on the link are capable of a higher data

rate.

cfg_link_ctrl2

16

Output

cfg_link_ctrl2[31:16]

is the secondary Link

Control register of the PCI Express capability

structure for Gen2 operation.

When

tl_cfg_addr=4'b0010

,

tl_cfg_ctl

returns

the primary and secondary Link Control registers,

{

{cfg_link_ctrl[15:0], cfg_link_

ctrl2[15:0]}

. The primary Link Status register

contents are available on

tl_cfg_sts[46:31]

.

For Gen1 variants, the link bandwidth notification

bit is always set to 0. For Gen2 variants, this bit is

set to 1.

cfg_prm_cmd_func

16

Output

Base/Primary Command register for the PCI

Configuration Space.

cfg_root_ctrl

8

Output

Root control and status register of the PCI Express

capability. This register is only available in Root

Port mode.

cfg_sec_ctrl

16

Output

Secondary bus Control and Status register of the

PCI Express capability. This register is available

only in Root Port mode.

cfg_secbus

8

Output

Secondary bus number. This register is available

only in Root Port mode.

cfg_subbus

8

Output

Subordinate bus number. This register is available

only in Root Port mode.

2014.12.15

Configuration Space Register Access

4-39

Interfaces and Signal Descriptions

Altera Corporation