Tlp packet formats with data payload – Altera Arria V Avalon-ST User Manual

Page 238

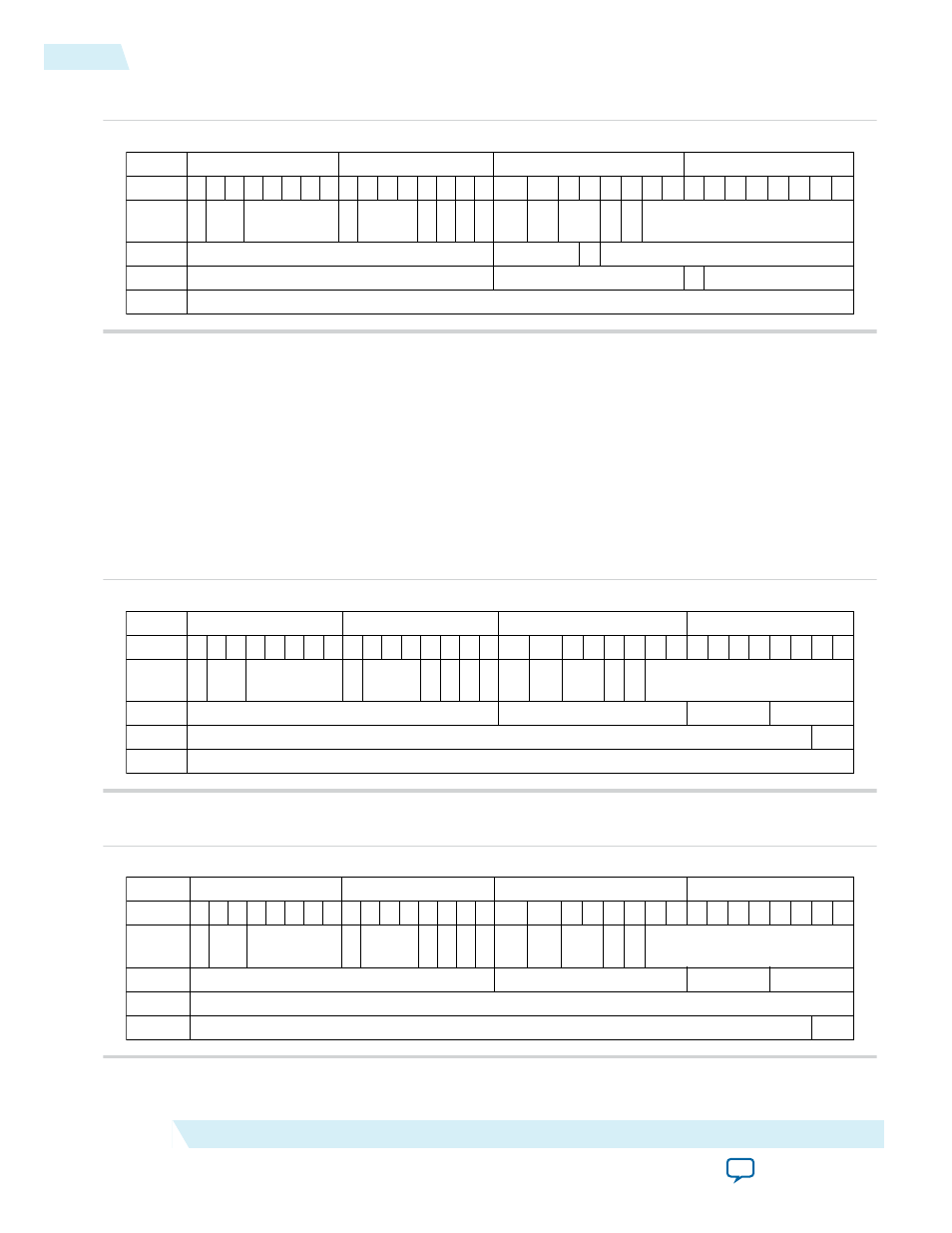

Figure A-9: Completion Locked without Data

Completion Locked without Data

3

+

2

+

1

+

0

+

7 6 5 4 3 2 1 0

7 6 5 4 3 2 1 0 7

6

5 4 3 2 1 0 7 6 5 4 3 2 1 0

Byte 0

0 0 0 0 1 0 1 1

0

TC

0 0 0 0

TD

EP

Att

r

0 0

Length

Byte 4

t

n

u

o

C

e

t

y

B

B

s

u

t

a

t

S

D

I

r

e

t

e

l

p

m

o

C

Byte 8

g

a

T

D

I

r

e

t

s

e

u

q

e

R

0

Lower Address

Byte 12

Reserved

Related Information

•

Data Alignment and Timing for the 64-Bit Avalon-ST RX Interface

•

Data Alignment and Timing for the 128-Bit Avalon-ST RX Interface

on page 4-10

•

Data Alignment and Timing for the 64-Bit Avalon-ST TX Interface

•

Data Alignment and Timing for the 128-Bit Avalon-ST TX Interface

on page 4-20

TLP Packet Formats with Data Payload

Figure A-10: Memory Write Request, 32-Bit Addressing

Memory Write Request, 32-Bit Addressing

3

+

2

+

1

+

0

+

7 6 5 4 3 2 1 0 7 6 5 4 3 2 1 0 7

6

5 4 3 2 1 0 7 6 5 4 3 2 1 0

Byte 0

0 1 0 0 0 0 0 0 0

TC

0 0 0 0

TD

EP

Att

r

0 0

Length

Byte 4

E

B

t

s

r

i

F

E

B

t

s

a

L

g

a

T

D

I

r

e

t

s

e

u

q

e

R

Byte 8

Address[31:2]

0 0

Byte 12

Reserved

Figure A-11: Memory Write Request, 64-Bit Addressing

Memory Write Request, 64-Bit Addressing

3

+

2

+

1

+

0

+

7 6 5 4 3 2 1 0 7 6

5 4 3 2 1 0 7

6

5 4 3 2 1 0 7 6 5 4 3 2 1 0

Byte 0

0 1 1 0 0 0 0 0 0

TC

0 0 0 0

TD

EP

Att

r

0 0

Length

Byte 4

E

B

t

s

r

i

F

E

B

t

s

a

L

g

a

T

D

I

r

e

t

s

e

u

q

e

R

Byte 8

Address[63:32]

Byte 12

Address[31:2]

0 0

A-4

TLP Packet Formats with Data Payload

2014.12.15

Altera Corporation

Transaction Layer Packet (TLP) Header Formats