Altera Arria V Avalon-ST User Manual

Page 77

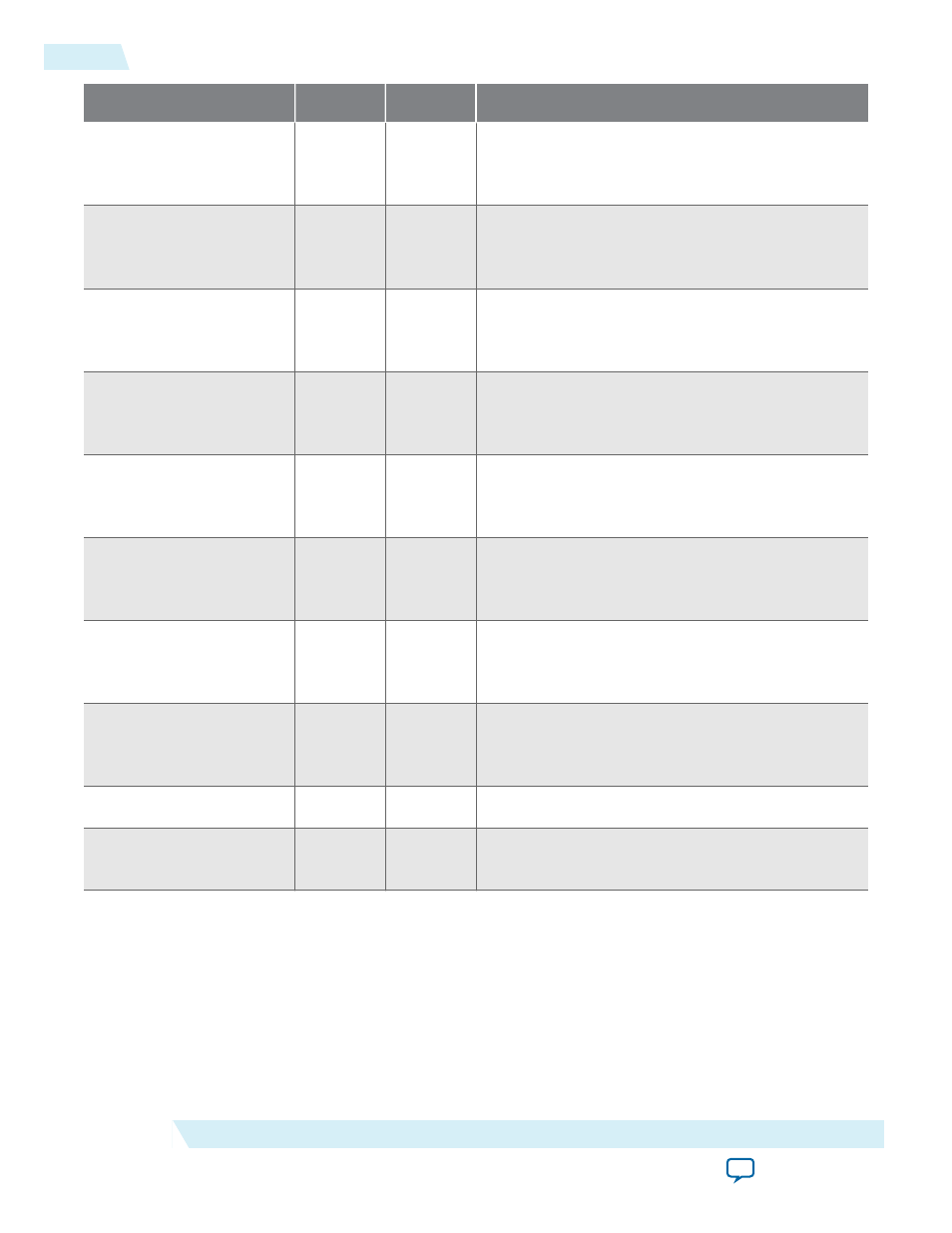

Register

Width

Direction

Description

cfg_msi_addr

64

Output

cfg_msi_add[63:32]

is the message signaled

interrupt (MSI) upper message address.

cfg_msi_

add[31:0]

is the MSI message address.

cfg_io_bas

20

Output

The upper 20 bits of the I/O limit registers of the

Type1 Configuration Space. This register is only

available in Root Port mode.

cfg_io_lim

20

Output

The upper 20 bits of the IO limit registers of the

Type1 Configuration Space. This register is only

available in Root Port mode.

cfg_np_bas

12

Output

The upper 12 bits of the memory base register of the

Type1 Configuration Space. This register is only

available in Root Port mode.

cfg_np_lim

12

Output

The upper 12 bits of the memory limit register of

the Type1 Configuration Space. This register is only

available in Root Port mode.

cfg_pr_bas

44

Output

The upper 44 bits of the prefetchable base registers

of the Type1 Configuration Space. This register is

only available in Root Port mode.

cfg_pr_lim

44

Output

The upper 44 bits of the prefetchable limit registers

of the Type1 Configuration Space. Available in Root

Port mode.

cfg_pmcsr

32

Output

cfg_pmcsr[31:16]

is Power Management Control

and

cfg_pmcsr[15:0]

is the Power Management

Status register.

cfg_msixcsr

16

Output

MSI-X message control.

cfg_msicsr

16

Output

MSI message control. Refer to the following table

for the fields of this register.

4-40

Configuration Space Register Access

2014.12.15

Altera Corporation

Interfaces and Signal Descriptions