Avalon-st tx interface – Altera Arria V Avalon-ST User Manual

Page 50

Figure 4-12: 128-Bit Avalon-ST Interface Back-to-Back Transmission

The following figure illustrates back-to-back transmission on the 128-bit Avalon-ST RX interface with no

idle cycles between the assertion of

rx_st_eop

and

rx_st_sop

.

pld_clk

rx_st_data[127:0]

rx_st_sop

rx_st_eop

rx_st_empty

rx_st_ready

rx_st_valid

rx_st_err

BB ... BB ... BB ... BB ... BB ... BB ... BB ... BB ... BB ... BB ... BB ... BB ...

...

BB

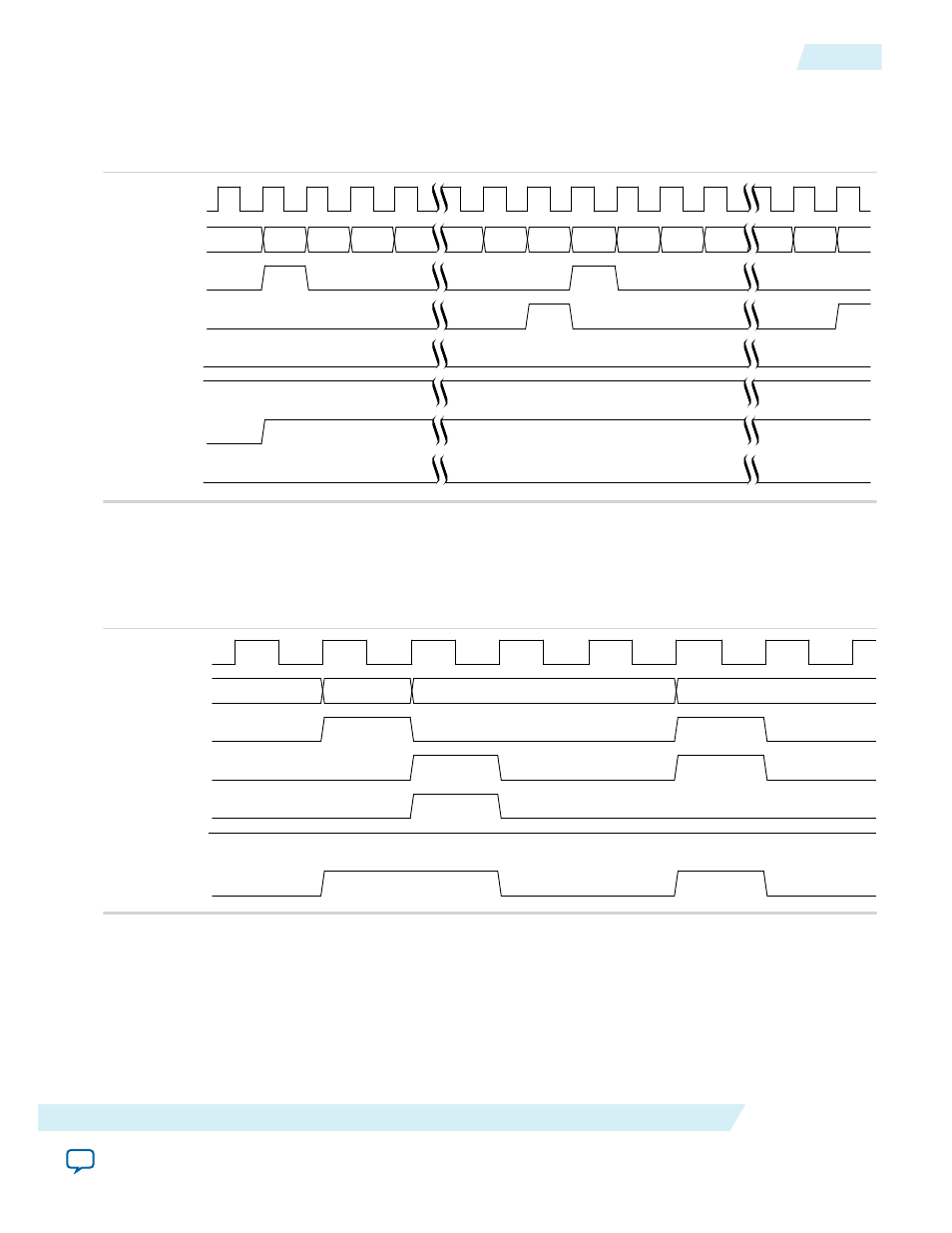

Figure 4-13: 128-Bit Packet Examples of rx_st_empty and Single-Cycle Packet

The following figure illustrates a two-cycle packet with valid data in the lower qword

(

rx_st_data[63:0]

) and a one-cycle packet where the

rx_st_sop

and

rx_st_eop

occur in the same

cycle.

pld_clk

rx_st_data[127:0]

rx_st_sop

rx_st_eop

rx_st_empty

rx_st_ready

rx_st_valid

0000090

1C0020000F0000000100004

450AC89000012FE0D10004

For a complete description of the TLP packet header formats, refer to Appendix A, Transaction Layer

Packet (TLP) Header Formats.

Avalon-ST TX Interface

The following table describes the signals that comprise the Avalon-ST TX Datapath. The TX data signal

can be 64 or 128.

2014.12.15

Avalon-ST TX Interface

4-13

Interfaces and Signal Descriptions

Altera Corporation