Altera Arria V Avalon-ST User Manual

Page 90

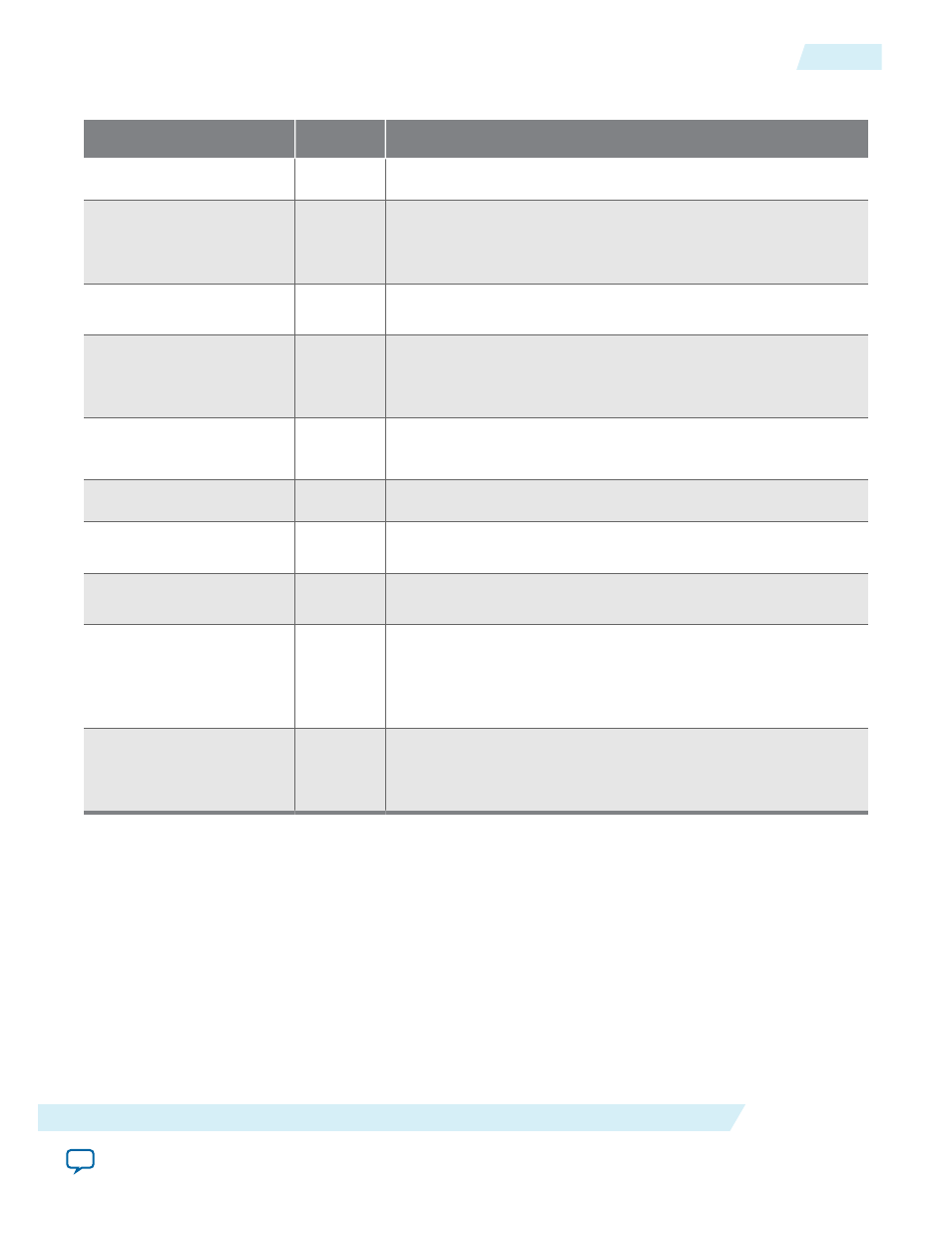

Table 4-23: Hard IP Reconfiguration Signals

Signal

Direction

Description

hip_reconfig_clk

Input

hip_reconfig_rst_n

Input

Active-low Avalon-MM reset. Resets all of the dynamic reconfi‐

guration registers to their default values as described in Hard IP

Reconfiguration Registers.

hip_reconfig_

address[9:0]

Input

The 10-bit reconfiguration address.

hip_reconfig_read

Input

Read signal. This interface is not pipelined. You must wait for the

return of the

hip_reconfig_readdata[15:0]

from the current

read before starting another read operation.

hip_reconfig_

readdata[15:0]

Output

16-bit read data.

hip_reconfig_readdata[15:0]

is valid on the

third cycle after the assertion of

hip_reconfig_read

.

hip_reconfig_write

Input

Write signal.

hip_reconfig_

writedata[15:0]

Input

16-bit write model.

hip_reconfig_byte_

en[1:0]

Input

Byte enables, currently unused.

ser_shift_load

Input

You must toggle this signal once after changing to user mode

before the first access to read-only registers. This signal should

remain asserted for a minimum of 324 ns after switching to user

mode.

interface_sel

Input

A selector which must be asserted when performing dynamic

reconfiguration. Drive this signal low 4 clock cycles after the

release of

ser_shif

t_load

.

2014.12.15

Hard IP Reconfiguration Interface

4-53

Interfaces and Signal Descriptions

Altera Corporation