Interrupts for endpoints – Altera Arria V Avalon-ST User Manual

Page 67

Interrupts for Endpoints

Refer to Interrupts for detailed information about all interrupt mechanisms.

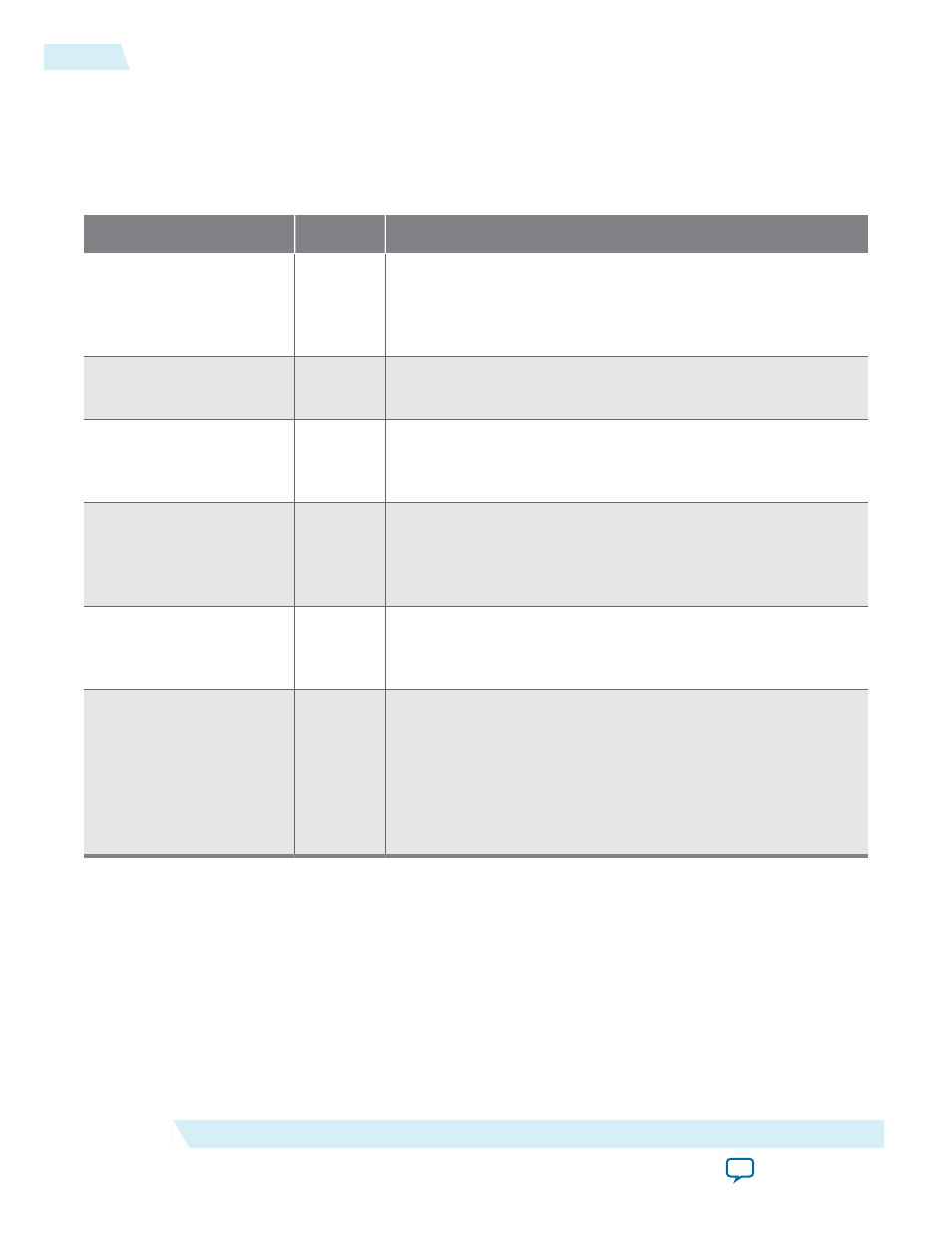

Table 4-9: Interrupt Signals for Endpoints

Signal

Direction

Description

app_msi_req

Input

Application Layer MSI request. Assertion causes an MSI posted

write TLP to be generated based on the MSI configuration

register values and the

app_msi_tc

and

app_msi_num

input

ports.

app_msi_ack

Output

Application Layer MSI acknowledge. This signal acknowledges

the Application Layer's request for an MSI interrupt.

app_msi_tc[2:0]

Input

Application Layer MSI traffic class. This signal indicates the

traffic class used to send the MSI (unlike INTX interrupts, any

traffic class can be used to send MSIs).

app_msi_num[4:0]

Input

MSI number of the Application Layer. This signal provides the

low order message data bits to be sent in the message data field of

MSI messages requested by

app_msi_req

. Only bits that are

enabled by the MSI Message Control register apply.

app_msi_func[2:0]

Input

Indicates which function is asserting an interrupt with 0

corresponding to function 0, 1 corresponding to function 1, and

so on.

app_int_sts[7:0]

Input

Level active interrupt signal. Bit 0 corresponds to function 0, and

so on. Drives the INTx line for that function. The core maps this

status to INT A/B/C/D according to the function

Interrupt_Pin

register. The core internally wire-ORs the INT requests from all

sources, and generates INT messages on the rising/falling edges

of the wire-ORed result. The core logs the

app_int_sts[7:0]

status in the function PCI Status register.

Related Information

•

on page 7-6

•

4-30

Interrupts for Endpoints

2014.12.15

Altera Corporation

Interfaces and Signal Descriptions