Altera Arria V Avalon-ST User Manual

Page 78

Register

Width

Direction

Description

cfg_tcvcmap

24

Output

Configuration traffic class (TC)/virtual channel

(VC) mapping. The Application Layer uses this

signal to generate a TLP mapped to the appropriate

channel based on the traffic class of the packet.

•

cfg_tcvcmap[2:0]

: Mapping for TC0 (always 0)

.

•

cfg_tcvcmap[5:3]

: Mapping for TC1.

•

cfg_tcvcmap[8:6]

: Mapping for TC2.

•

cfg_tcvcmap[11:9]

: Mapping for TC3.

•

cfg_tcvcmap[14:12]

: Mapping for TC4.

•

cfg_tcvcmap[17:15]

: Mapping for TC5.

•

cfg_tcvcmap[20:18]

: Mapping for TC6.

•

cfg_tcvcmap[23:21]

: Mapping for TC7.

cfg_msi_data

16

Output

cfg_msi_data[15:0]

is message data for MSI.

cfg_busdev

13

Output

Bus/Device Number captured by or programmed in

the Hard IP.

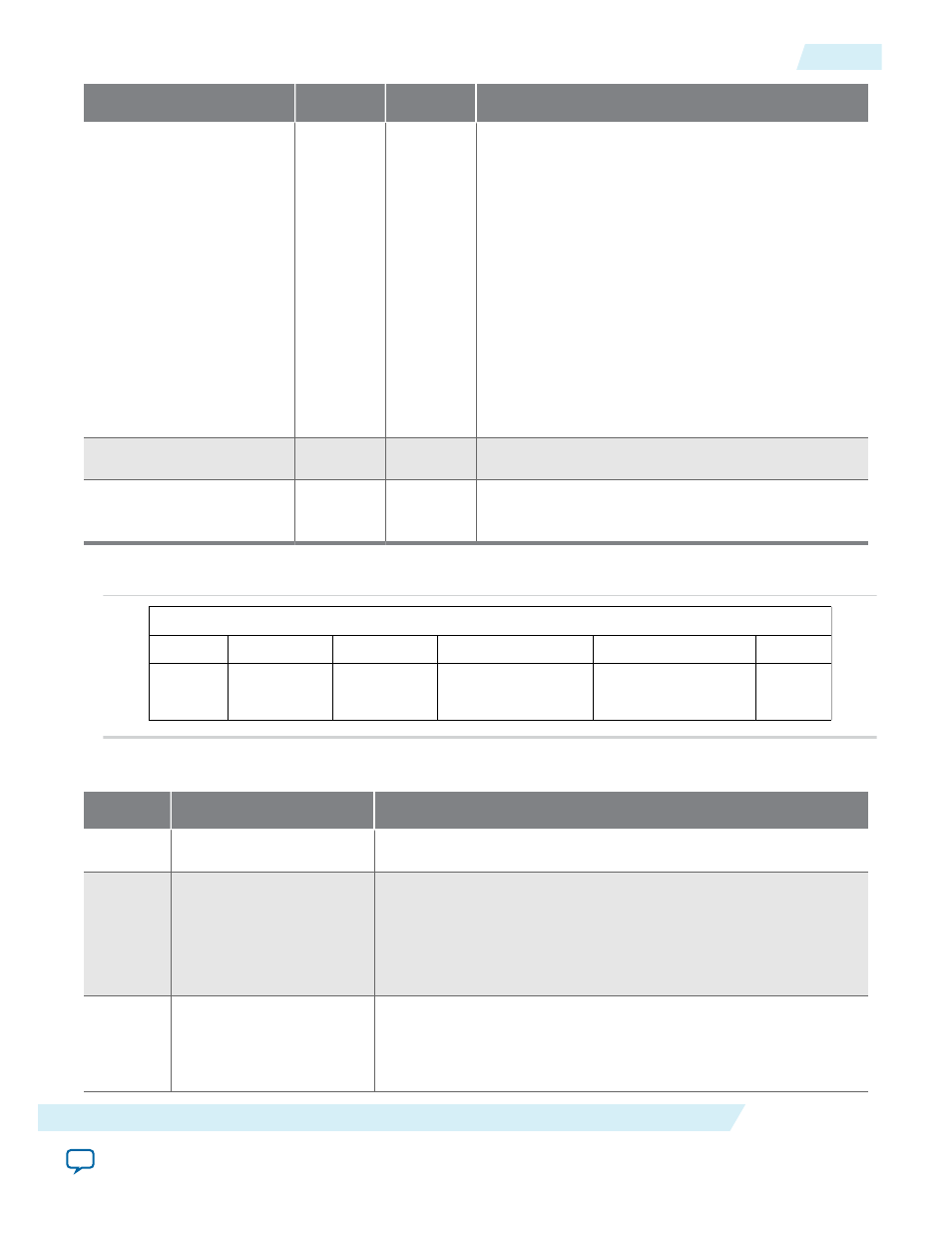

Figure 4-29: Configuration MSI Control Status Register

Field and Bit Map

0

1

3

4

6

7

8

9

5

1

reserved

mask

capability

64-bit

address

capability

multiple message enable multiple message capable

MSI

enable

Table 4-15: Configuration MSI Control Status Register Field Descriptions

Bit(s)

Field

Description

[15:9]

Reserved

N/A

[8]

mask capability

Per-vector masking capable. This bit is hardwired to 0 because the

function does not support the optional MSI per-vector masking

using the

Mask_Bits

and

Pending_Bits

registers defined in the

PCI Local Bus Specification. Per-vector masking can be

implemented using Application Layer registers.

[7]

64-bit address

capability

64-bit address capable.

• 1: function capable of sending a 64-bit message address

• 0: function not capable of sending a 64-bit message address

2014.12.15

Configuration Space Register Access

4-41

Interfaces and Signal Descriptions

Altera Corporation