Link capabilities – Altera Arria V Avalon-ST User Manual

Page 27

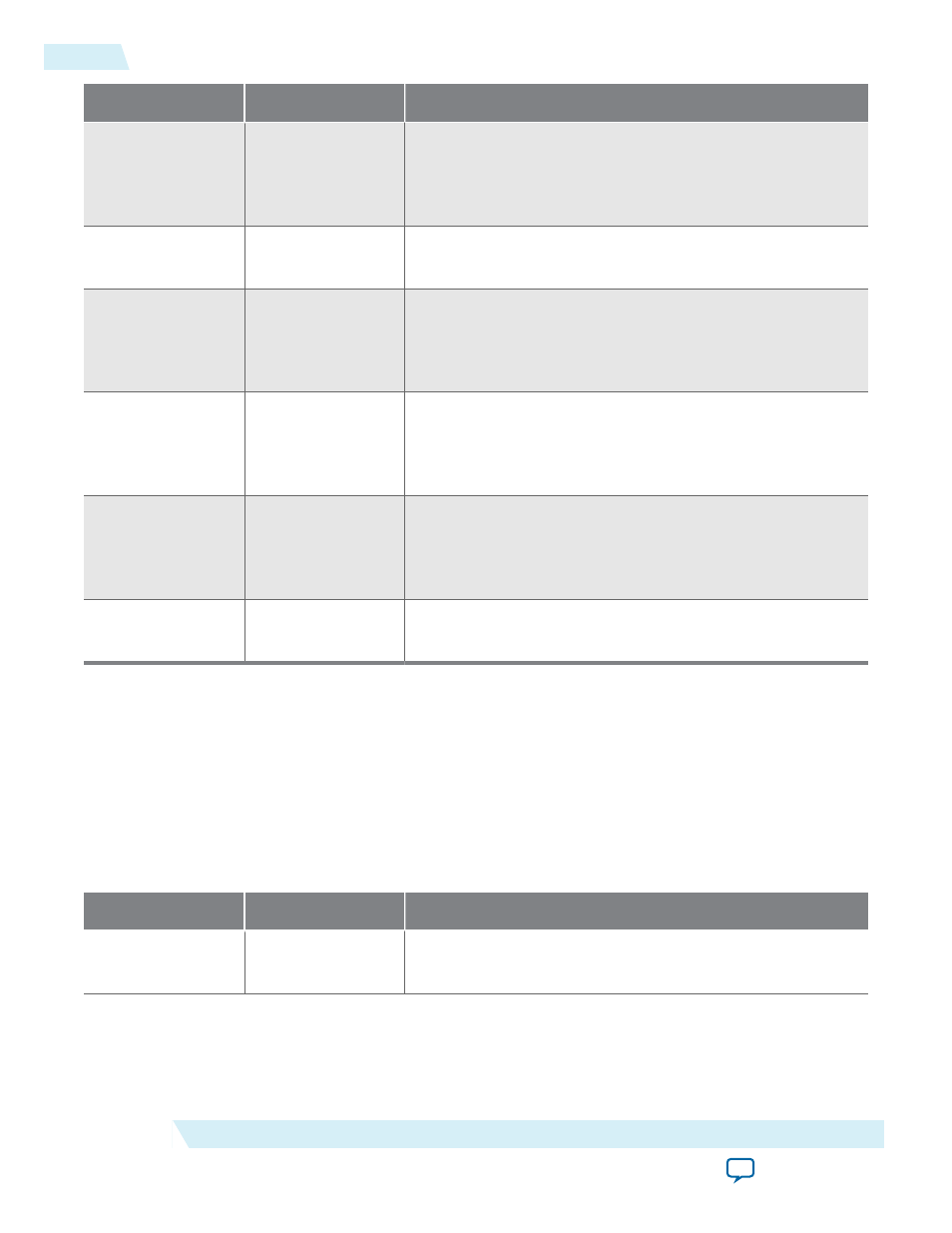

Parameter

Value

Description

Reference clock

frequency

100 MHz

125 MHz

The PCI Express Base Specification requires a

100 MHz ±300 ppm reference clock. The 125 MHz reference

clock is provided as a convenience for systems that include a

125 MHz clock source.

Use 62.5 MHz

application clock

On/Off

This mode is only available only for Gen1 ×1.

Use deprecated

RX Avalon-ST

data byte enable

port (rx_st_be)

On/Off

This parameter is only available for the Avalon-ST Arria V

Hard IP for PCI Express.

Enable configu‐

ration via PCIe

link

On/Off

When On, the Quartus II software places the Endpoint in the

location required for configuration via protocol (CvP). For

more information about CvP, click the Configuration via

Protocol (CvP) link below.

Enable Hard IP

Reconfiguration

On/Off

When On, you can use the Hard IP reconfiguration bus to

dynamically reconfigure Hard IP read-only registers. For more

information refer to Hard IP Reconfiguration Interface. This

parameter is not available for the Avalon-MM IP Cores.

Number of

Functions

1–8

Specifies the number of functions that share the same link.

Related Information

•

Configuration via Protocol (CvP)

•

•

Link Capabilities

Table 3-2: Link Capabilities

Parameter

Value

Description

Link port

number

0x01

Sets the read-only value of the port number field in the

Link

Capabilities Register

.

3-4

Link Capabilities

2014.12.15

Altera Corporation

Parameter Settings