Altera Arria V Avalon-ST User Manual

Page 120

Figure 7-1: MSI Handler Block

MSI Handler

Block

app_msi_req

app_msi_ack

app_msi_tc[2:0]

app_msi_num[4:0]

app_msi_func[2:0]

app_int_sts_vec[7:0]

cfg_msicsr[15:0]

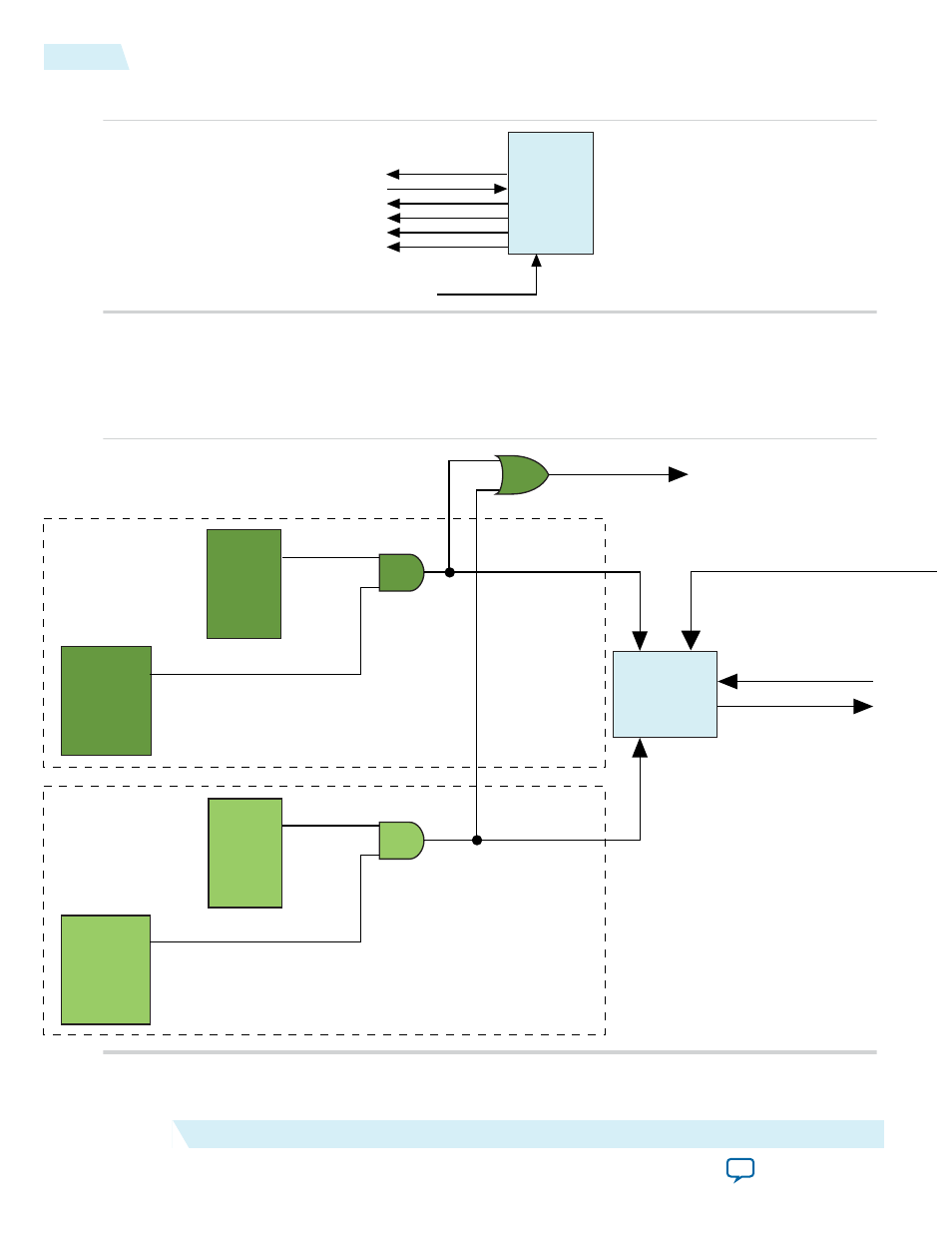

The following figure illustrates a possible implementation of the MSI handler block with a per vector

enable bit. A global Application Layer interrupt enable can also be implemented instead of this per vector

MSI.

Figure 7-2: Example Implementation of the MSI Handler Block

app_int_en0

app_int_sts0

app_msi_req0

app_int_en1

app_int_sts1

app_msi_req1

app_int_sts

MSI

Arbitration

msi_enable & Master Enable

app_msi_req

app_msi_ack

Vector 1

Vector 0

IRQ

Generation

App Layer

IRQ

Generation

App Layer

R/W

R/W

7-2

MSI Interrupts

2014.12.15

Altera Corporation

Interrupts

This manual is related to the following products: