Uncorrectable internal error mask register – Altera Arria V Avalon-ST User Manual

Page 108

Bits

Register Description

Reset Value

Access

[1]

START_XFER

. Sets the CvP output to the FPGA control block

indicating the start of a transfer.

1’b0

RW

[0]

CVP_CONFIG

. When asserted, instructs that the FPGA control

block begin a transfer via CvP.

1’b0

RW

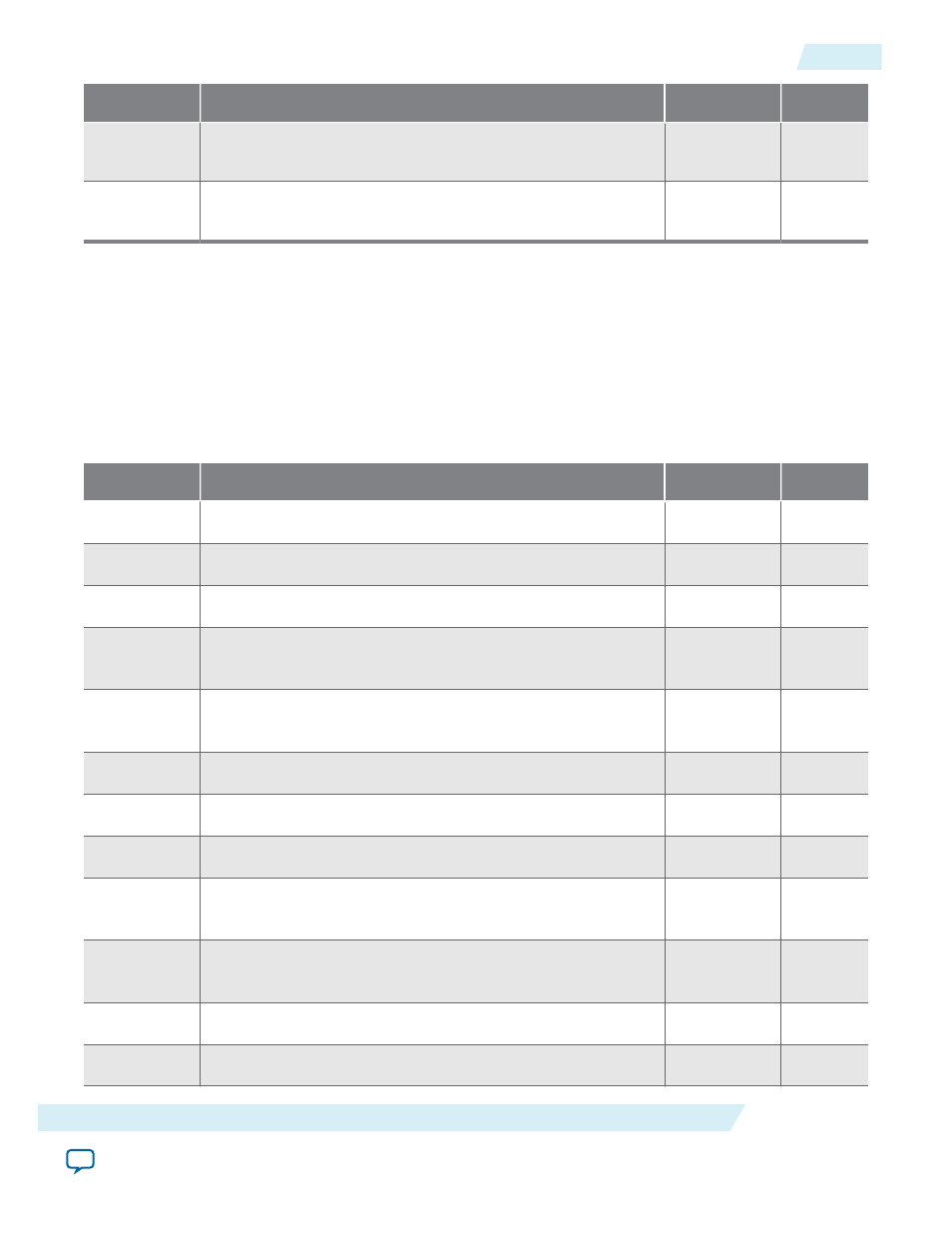

Uncorrectable Internal Error Mask Register

Table 5-11: Uncorrectable Internal Error Mask Register

The

Uncorrectable Internal Error Mask

register controls which errors are forwarded as internal

uncorrectable errors. With the exception of the configuration error detected in CvP mode, all of the errors are

severe and may place the device or PCIe link in an inconsistent state. The configuration error detected in CvP

mode may be correctable depending on the design of the programming software. The access code RWS stands for

Read Write Sticky meaning the value is retained after a soft reset of the IP core.

Bits

Register Description

Reset Value

Access

[31:12]

Reserved.

1b’0

RO

[11]

Mask for RX buffer posted and completion overflow error.

1b’1

RWS

[10]

Reserved

1b’0

RO

[9]

Mask for parity error detected on Configuration Space to TX bus

interface.

1b’1

RWS

[8]

Mask for parity error detected on the TX to Configuration Space

bus interface.

1b’1

RWS

[7]

Mask for parity error detected at TX Transaction Layer error.

1b’1

RWS

[6]

Reserved

1b’0

RO

[5]

Mask for configuration errors detected in CvP mode.

1b’0

RWS

[4]

Mask for data parity errors detected during TX Data Link LCRC

generation.

1b’1

RWS

[3]

Mask for data parity errors detected on the RX to Configuration

Space Bus interface.

1b’1

RWS

[2]

Mask for data parity error detected at the input to the RX Buffer.

1b’1

RWS

[1]

Mask for the retry buffer uncorrectable ECC error.

1b’1

RWS

2014.12.15

Uncorrectable Internal Error Mask Register

5-13

Registers

Altera Corporation