Generating quartus ii synthesis files, Understanding the files generated, Compiling the design in the quartus ii software – Altera Arria V Avalon-ST User Manual

Page 18

Generating Quartus II Synthesis Files

1. On the Generate menu, select Generate HDL.

2. For Create HDL design files for synthesis, select Verilog.

You can leave the default settings for all other items.

3. Click Generate to generate files for Quartus II synthesis.

4. Click Finish when the generation completes.

Understanding the Files Generated

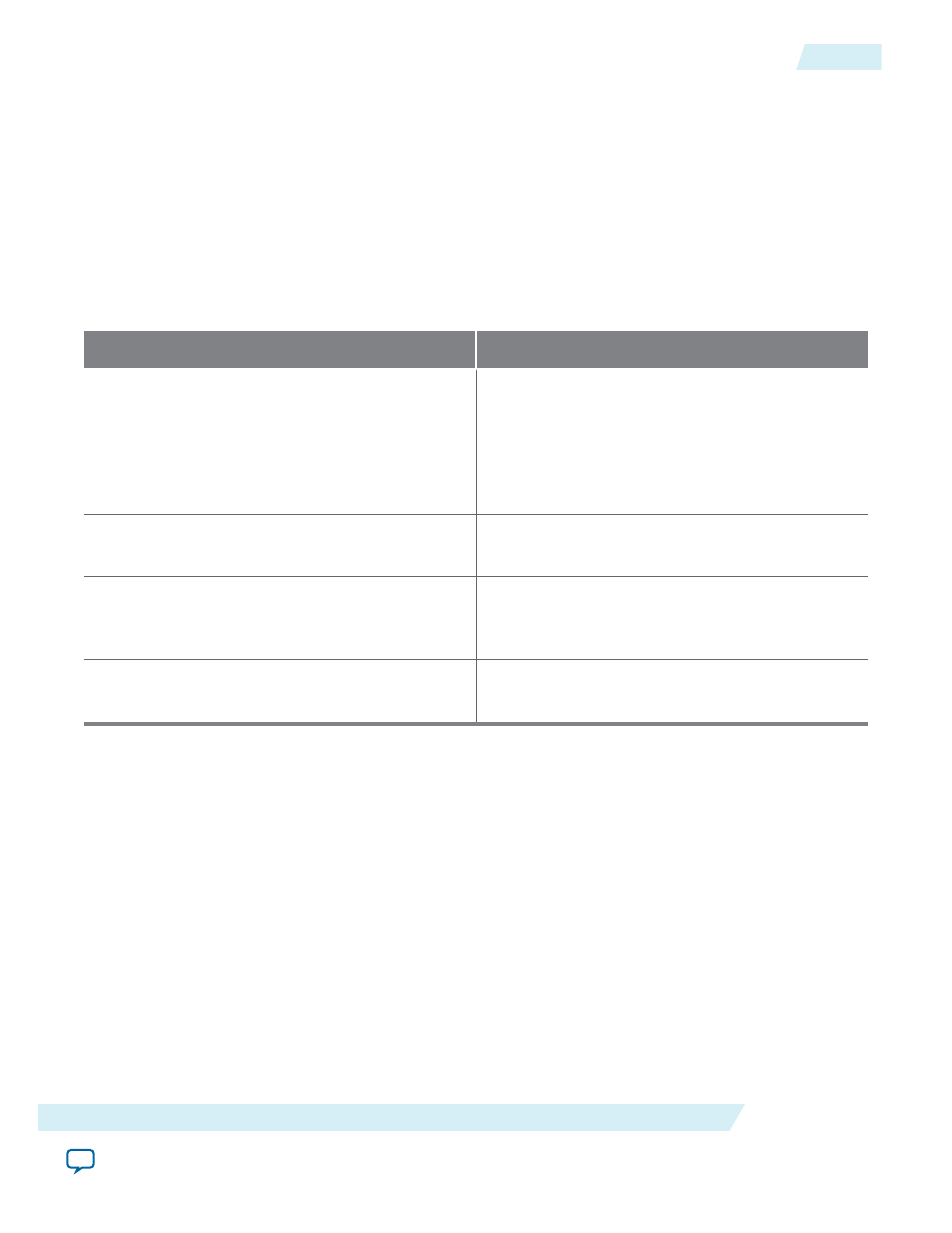

Table 2-2: Overview of Qsys Generation Output Files

Directory

Description

Includes the top-level HDL file for the Hard IP for

PCI Express and the .qip file that lists all of the

necessary assignments and information required to

process the IP core in the Quartus II compiler.

Generally, a single .qip file is generated for each IP

core.

Includes the HDL files necessary for Quartus II

synthesis.

Includes testbench subdirectories for the Aldec,

Cadence, Synopsys, and Mentor simulation tools

with the required libraries and simulation scripts.

Includes the HDL source files and scripts for the

simulation testbench.

For a more detailed listing of the directories and files the Quartus II software generates, refer to Files

Generated for Altera IP Cores in Compiling the Design in the Qsys Design Flow.

Understanding Physical Placement of the PCIe IP Core

For more information about physical placement of the PCIe blocks, refer to the links below. Contact your

Altera sales representative for detailed information about channel and PLL usage.

Related Information

•

Physical Layout of Hard IP in Arria V Devices

on page 4-49

•

Channel Placement in Arria V Devices

Compiling the Design in the Quartus II Software

To compile the Qsys design example in the Quartus II software, you must create a Quartus II project and

add your Qsys files to that project.

2014.12.15

Generating Quartus II Synthesis Files

2-5

Getting Started with the Arria V Hard IP for PCI Express

Altera Corporation