Altera Arria V Avalon-ST User Manual

Page 197

configuration is unlikely to be useful in real systems. If the procedure is unable to assign the BARs,

it displays an error message and stops the simulation.

4. Based on the above BAR assignments, the Root Port Configuration Space address windows are

assigned to encompass the valid BAR address ranges.

5. The Endpoint PCI control register is set to enable master transactions, memory address decoding, and

I/O address decoding.

The

ebfm_cfg_rp_ep

procedure also sets up a

bar_table

data structure in BFM shared memory that lists

the sizes and assigned addresses of all Endpoint BARs. This area of BFM shared memory is write-

protected, which means any user write accesses to this area cause a fatal simulation error. This data

structure is then used by subsequent BFM procedure calls to generate the full PCI Express addresses for

read and write requests to particular offsets from a BAR. This procedure allows the testbench code that

accesses the Endpoint Application Layer to be written to use offsets from a BAR and not have to keep

track of the specific addresses assigned to the BAR. The following table shows how those offsets are used.

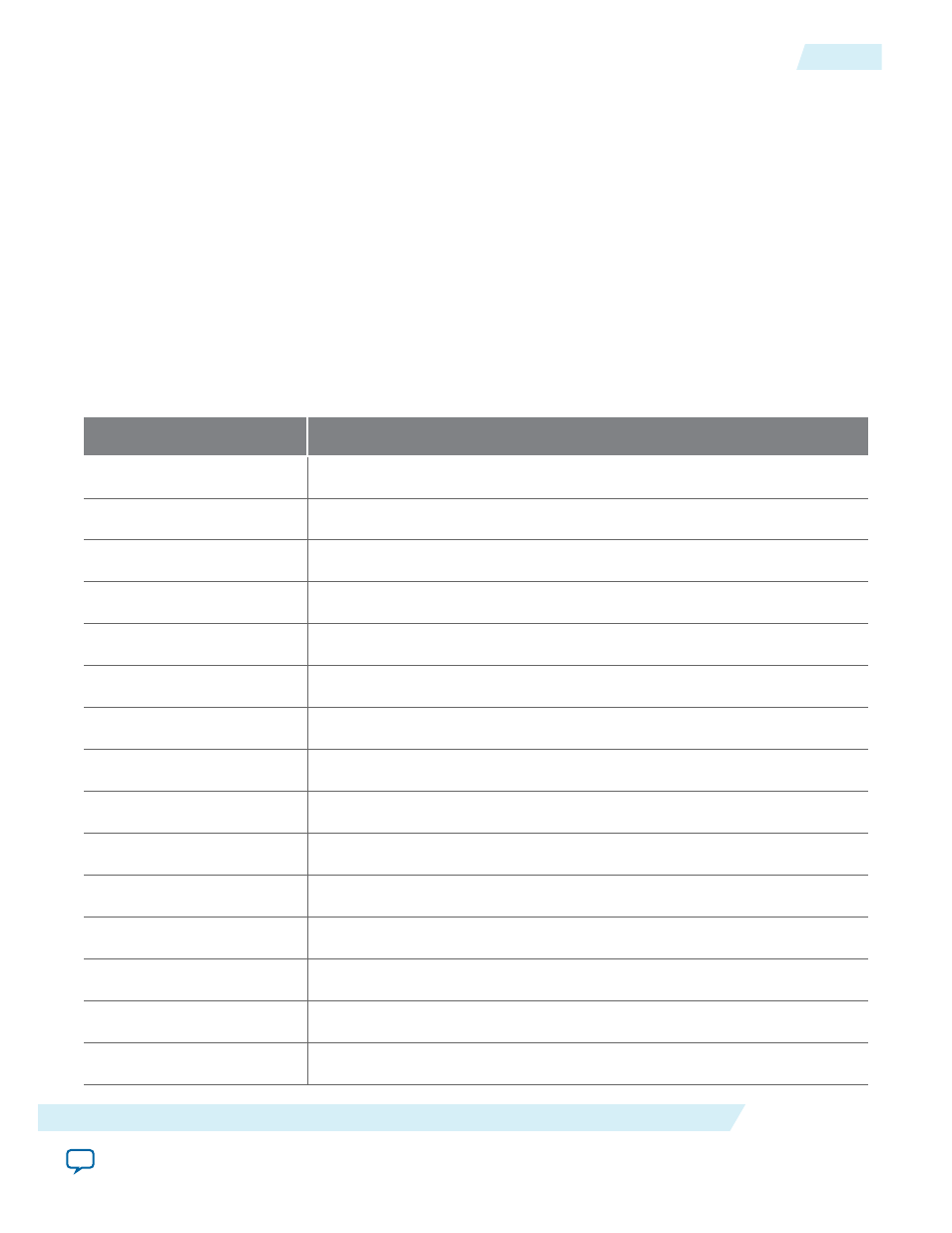

Table 16-19: BAR Table Structure

Offset (Bytes)

Description

+0

PCI Express address in BAR0

+4

PCI Express address in BAR1

+8

PCI Express address in BAR2

+12

PCI Express address in BAR3

+16

PCI Express address in BAR4

+20

PCI Express address in BAR5

+24

PCI Express address in Expansion ROM BAR

+28

Reserved

+32

BAR0 read back value after being written with all 1’s (used to compute size)

+36

BAR1 read back value after being written with all 1’s

+40

BAR2 read back value after being written with all 1’s

+44

BAR3 read back value after being written with all 1’s

+48

BAR4 read back value after being written with all 1’s

+52

BAR5 read back value after being written with all 1’s

+56

Expansion ROM BAR read back value after being written with all 1’s

2014.12.15

Configuration of Root Port and Endpoint

16-27

Testbench and Design Example

Altera Corporation