Channel placement in arria v devices, Hard ip reconfiguration interface – Altera Arria V Avalon-ST User Manual

Page 89

For more comprehensive information about Arria V transceivers, refer to the Transceiver Banks section in

the Transceiver Architecture in Arria V Devices.

Related Information

Channel Placement in Arria V Devices

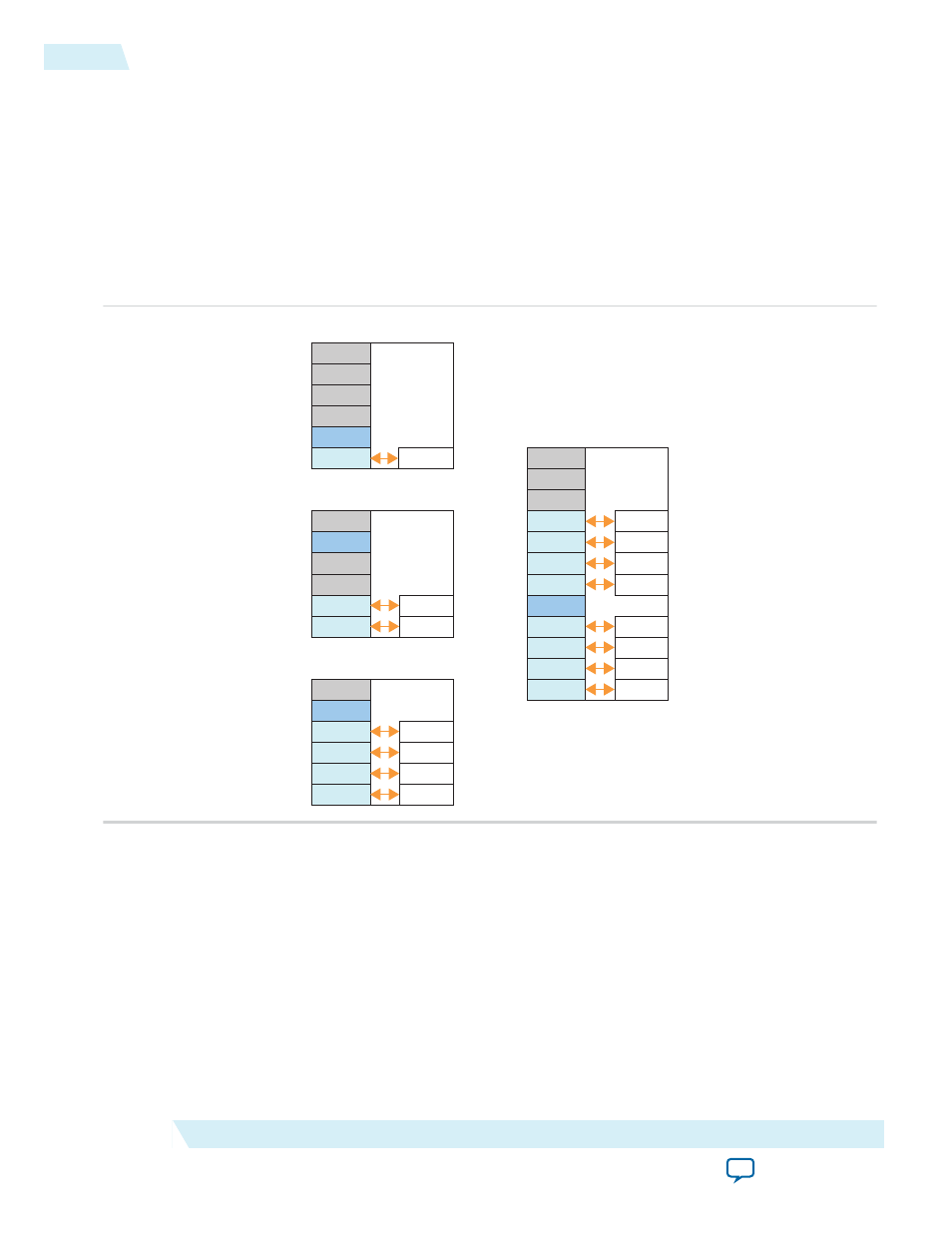

Figure 4-37: Arria V Gen1 and Gen2 Channel Placement Using the CMU PLL

In the following figures the channels shaded in blue provide the transmit CMU PLL generating the high-

speed serial clock.

Ch5

Ch3

Ch2

Ch1

Ch0

CMU PLL

PCIe Hard IP

Ch0

Ch1

Ch5

Ch3

Ch2

Ch1

Ch0

CMU PLL

PCIe Hard IP

Ch0

Ch1

Ch2

Ch3

Ch5

Ch3

Ch2

Ch1

Ch0

CMU PLL

Ch0

Ch1

Ch2

Ch3

Ch11

Ch9

Ch8

Ch7

Ch6

Ch10

PCIe Hard IP

Ch5

Ch6

Ch7

Ch4

Ch5

Ch3

Ch2

CMU PLL

Ch0

Ch4

PCIe Hard IP

x1

x8

x2

x4

Ch0

You can assign other protocols to unused channels the if data rate and clock specification exactly match

the PCIe configuration.

Hard IP Reconfiguration Interface

The Hard IP reconfiguration interface is an Avalon-MM slave interface with a 10-bit address and 16-bit

data bus. You can use this bus to dynamically modify the value of configuration registers that are read-

only at run time. To ensure proper system operation, reset or repeat device enumeration of the PCI

Express link after changing the value of read-only configuration registers of the Hard IP.

For an example that illustrates how to use this interface, refer to PCI SIG Gen2 x8 Merged Design - Stratix

V on the Altera wiki. The Related Information section below provides a link to this example.

4-52

Channel Placement in Arria V Devices

2014.12.15

Altera Corporation

Interfaces and Signal Descriptions