Base and limit registers for root ports, Device identification registers for function Page 34

Page 34

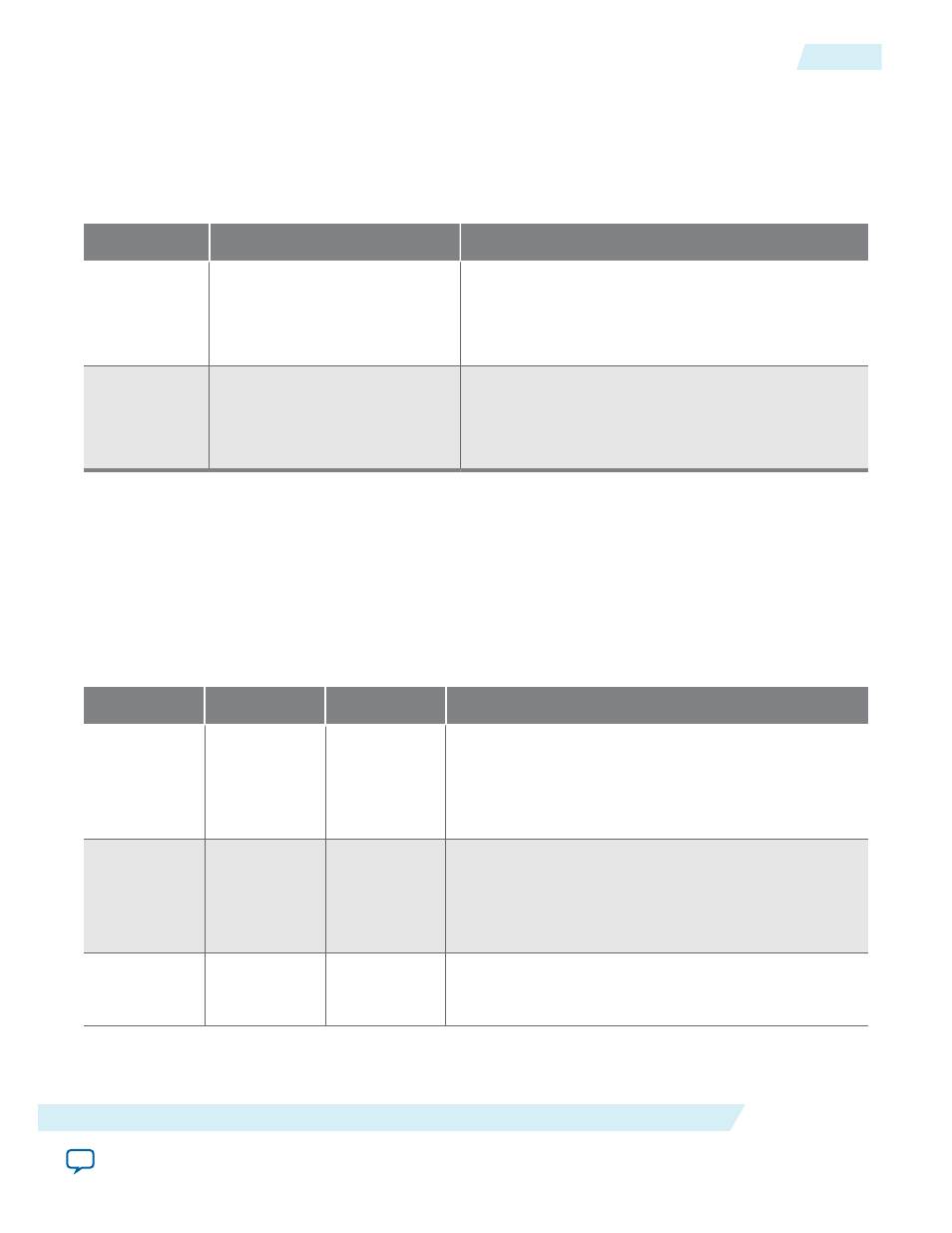

Base and Limit Registers for Root Ports

Table 3-9: Base and Limit Registers for Function 0

The following table describes the

Base

and

Limit

registers which are available in the Type 1 Configuration Space

for Root Ports. These registers are used for TLP routing and specify the address ranges assigned to components

that are downstream of the Root Port or bridge.

Parameter

Value

Description

Input/

Output

Disabled

16-bit I/O addressing

32-bit I/O addressing

Specifies the address widths for the

IO base

and

IO

limit

registers.

Prefetchable

memory

Disabled

16-bit memory addressing

32-bit memory addressing

Specifies the address widths for the

Prefetchable

Memory Base

register and

Prefetchable Memory

Limit

register.

Related Information

Device Identification Registers for Function

Table 3-10: Device ID Registers

The following table lists the default values of the read-only Device ID registers. You can use the parameter editor

to change the values of these registers. Refer to Type 0 Configuration Space Registers for the layout of the Device

Identification registers.

Register Name

Range

Default Value

Description

Vendor ID

16 bits

0x00000000

Sets the read-only value of the

Vendor ID

register. This

parameter cannot be set to 0xFFFF, per the PCI Express

Specification.

Address offset: 0x000.

Device ID

16 bits

0x00000001

Sets the read-only value of the

Device ID

register. This

register is only valid in the Type 0 (Endpoint) Configu‐

ration Space.

Address offset: 0x000.

Revision ID

8 bits

0x00000001

Sets the read-only value of the

Revision ID

register.

Address offset: 0x008.

2014.12.15

Base and Limit Registers for Root Ports

3-11

Parameter Settings

Altera Corporation