Transceiver reconfiguration – Altera Arria V Avalon-ST User Manual

Page 85

Transceiver Reconfiguration

Dynamic reconfiguration compensates for variations due to process, voltage and temperature (PVT).

Among the analog settings that you can reconfigure are V

OD

, pre-emphasis, and equalization.

You can use the Altera Transceiver Reconfiguration Controller to dynamically reconfigure analog

settings. For Gen2 operation, you must turn on Enable duty cycle calibration in the Transceiver Reconfi‐

guration Controller GUI. Arria V devices require duty cycle calibration (DCD) for data rates greater than

4.9152 Gbps. For more information about instantiating the Altera Transceiver Reconfiguration Controller

IP core refer to Hard IP Reconfiguration .

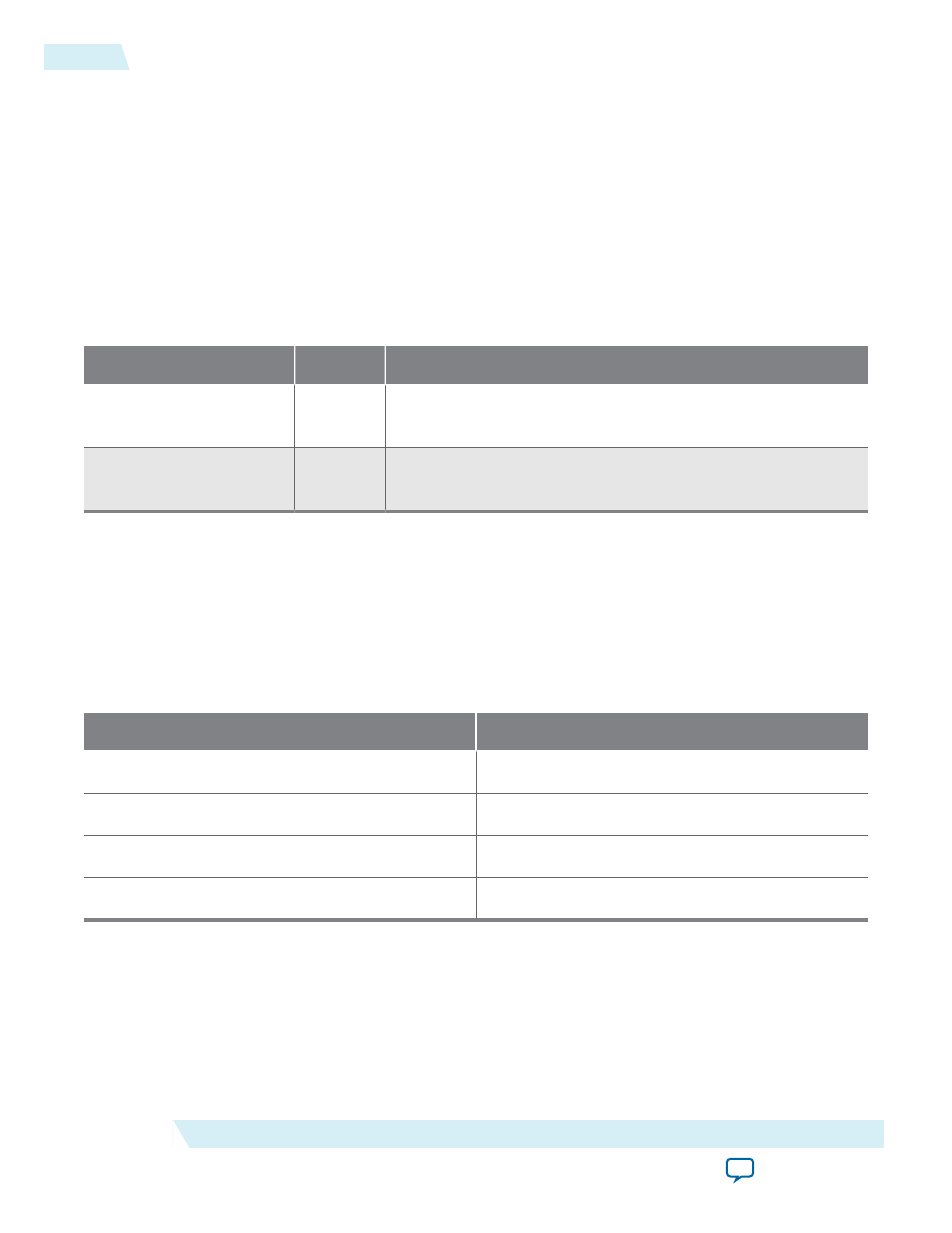

Table 4-19: Transceiver Control Signals

In this table,

Signal Name

Direction

Description

reconfig_from_

xcvr[(

Output

Reconfiguration signals to the Transceiver Reconfiguration

Controller.

reconfig_to_xcvr[(

70)-1:0]

Input

Reconfiguration signals from the Transceiver Reconfiguration

Controller.

The following table shows the number of logical reconfiguration and physical interfaces required for

various configurations. The Quartus II Fitter merges logical interfaces to minimize the number of physical

interfaces configured in the hardware. Typically, one logical interface is required for each channel and one

for each PLL.

The ×8 variants require an extra channel for PCS clock routing and control. The ×8 variants use channel 4

for clocking.

Table 4-20: Number of Logical and Physical Reconfiguration Interfaces

Variant

Logical Interfaces

Gen1 and Gen2 ×1

2

Gen1 and Gen2 ×2

3

Gen1 and Gen2 ×4

5

Gen1 ×8

10

For more information about the Transceiver Reconfiguration Controller, refer to the Transceiver Reconfi‐

guration Controller chapter in the Altera Transceiver PHY IP Core User Guide .

Related Information

4-48

Transceiver Reconfiguration

2014.12.15

Altera Corporation

Interfaces and Signal Descriptions