Altera Arria V Avalon-ST User Manual

Page 22

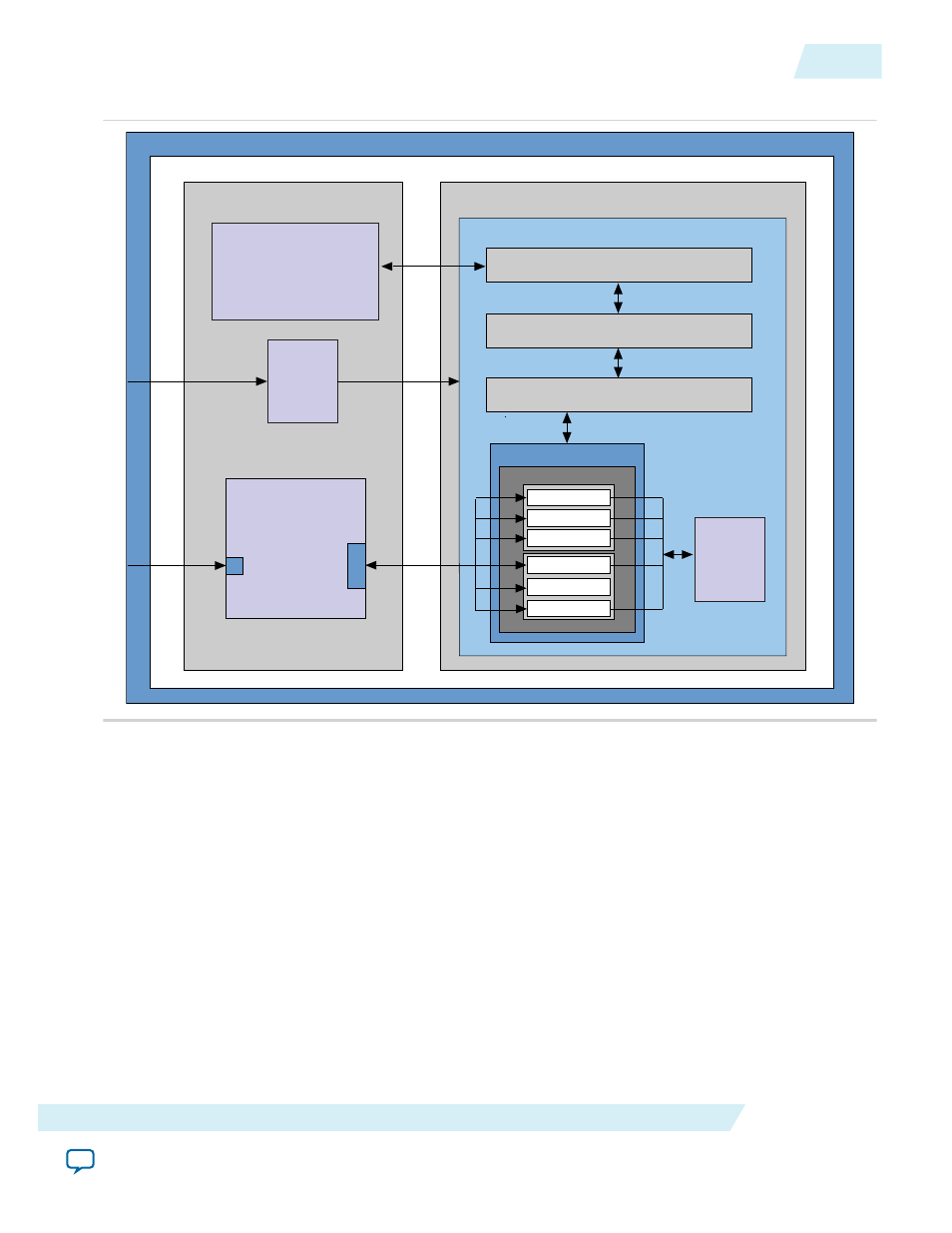

Figure 2-4: Testbench for PCI Express

PCB

Avalon-MM slave

Reset

Hard IP for PCI Express

Altera FPGA

PCB

Transaction Layer

Data Link Layer

PHY MAC Layer

x4 PCIe Link

(Physical Layer)

PHY IP Core for PCI Express

Lane 2

Lane 3

Lane 4

Lane 1

Lane 0

TX PLL

Transceiver Bank

S

Reconfig

to and from

Transceiver

to and from

Embedded

Controller

(Avalon-MM

slave interface)

Transceiver

Reconfiguration

Controller

Root

Port

BFM

npor

Reset

APPS

DUT

Chaining DMA

(User Application)

Using the IP Catalog To Generate Your Arria V Hard IP for PCI Express as a

Separate Component

You can also instantiate the Arria V Hard IP for PCI Express IP Core as a separate component for

integration into your project.

You can use the Quartus II IP Catalog and IP Parameter Editor to select, customize, and generate files

representing your custom IP variation. The IP Catalog (Tools > IP Catalog) automatically displays IP

cores available for your target device. Double-click any IP core name to launch the parameter editor and

generate files representing your IP variation.

For more information about the customizing and generating IP Cores refer to Specifying IP Core

Parameters and Options in Introduction to Altera IP Cores. For more information about upgrading older

IP cores to the current release, refer to Upgrading Outdated IP Cores in Introduction to Altera IP Cores.

2014.12.15

Using the IP Catalog To Generate Your Arria V Hard IP for PCI Express as a Separate

Component

2-9

Getting Started with the Arria V Hard IP for PCI Express

Altera Corporation