Altera Arria V Avalon-ST User Manual

Page 194

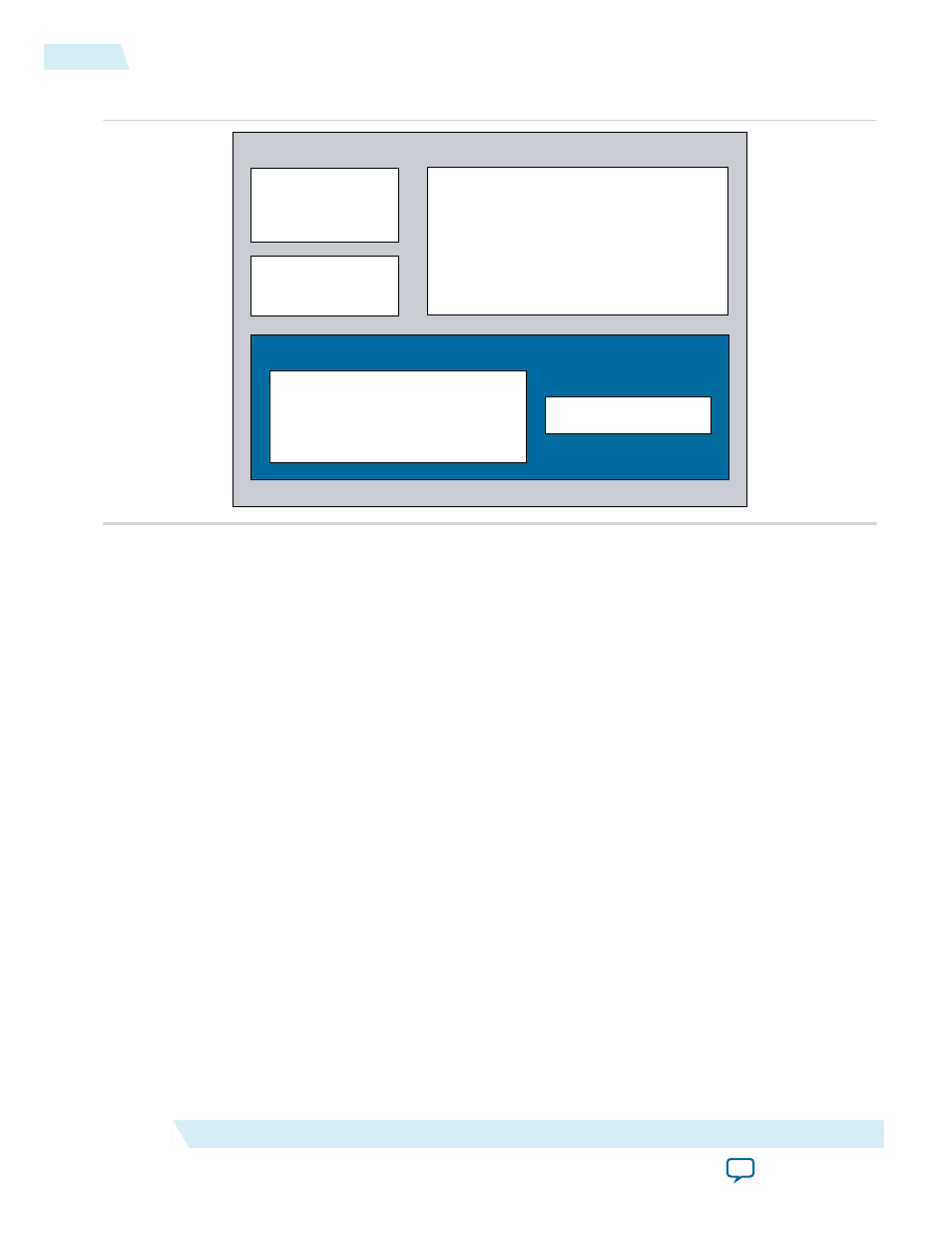

Figure 16-4: Root Port BFM

BFM Shared Memory

(altpcietb_bfm_shmem

_common)

BFM Log Interface

(altpcietb_bfm_log

_common)

Root Port RTL Model (altpcietb_bfm_rp_top_x8_pipen1b)

IP Functional Simulation

Model of the Root

Port Interface

(altpcietb_bfm_driver_rp)

Avalon-ST Interface

(altpcietb_bfm_vc_intf)

Root Port BFM

BFM Read/Write Shared Request Procedures

BFM Configuration Procedures

BFM Request Interface

(altpcietb_bfm_req_intf_common)

The functionality of each of the modules included is explained below.

• BFM shared memory (

altpcietb_bfm_shmem_common

Verilog HDL include file)—The Root Port BFM is

based on the BFM memory that is used for the following purposes:

• Storing data received with all completions from the PCI Express link.

• Storing data received with all write transactions received from the PCI Express link.

• Sourcing data for all completions in response to read transactions received from the PCI Express link.

• Sourcing data for most write transactions issued to the PCI Express link. The only exception is certain

BFM write procedures that have a four-byte field of write data passed in the call.

• Storing a data structure that contains the sizes of and the values programmed in the BARs of the

Endpoint.

A set of procedures is provided to read, write, fill, and check the shared memory from the BFM driver. For

details on these procedures, see BFM Shared Memory Access Procedures.

16-24

Root Port BFM

2014.12.15

Altera Corporation

Testbench and Design Example