Altera Arria V Avalon-ST User Manual

Page 141

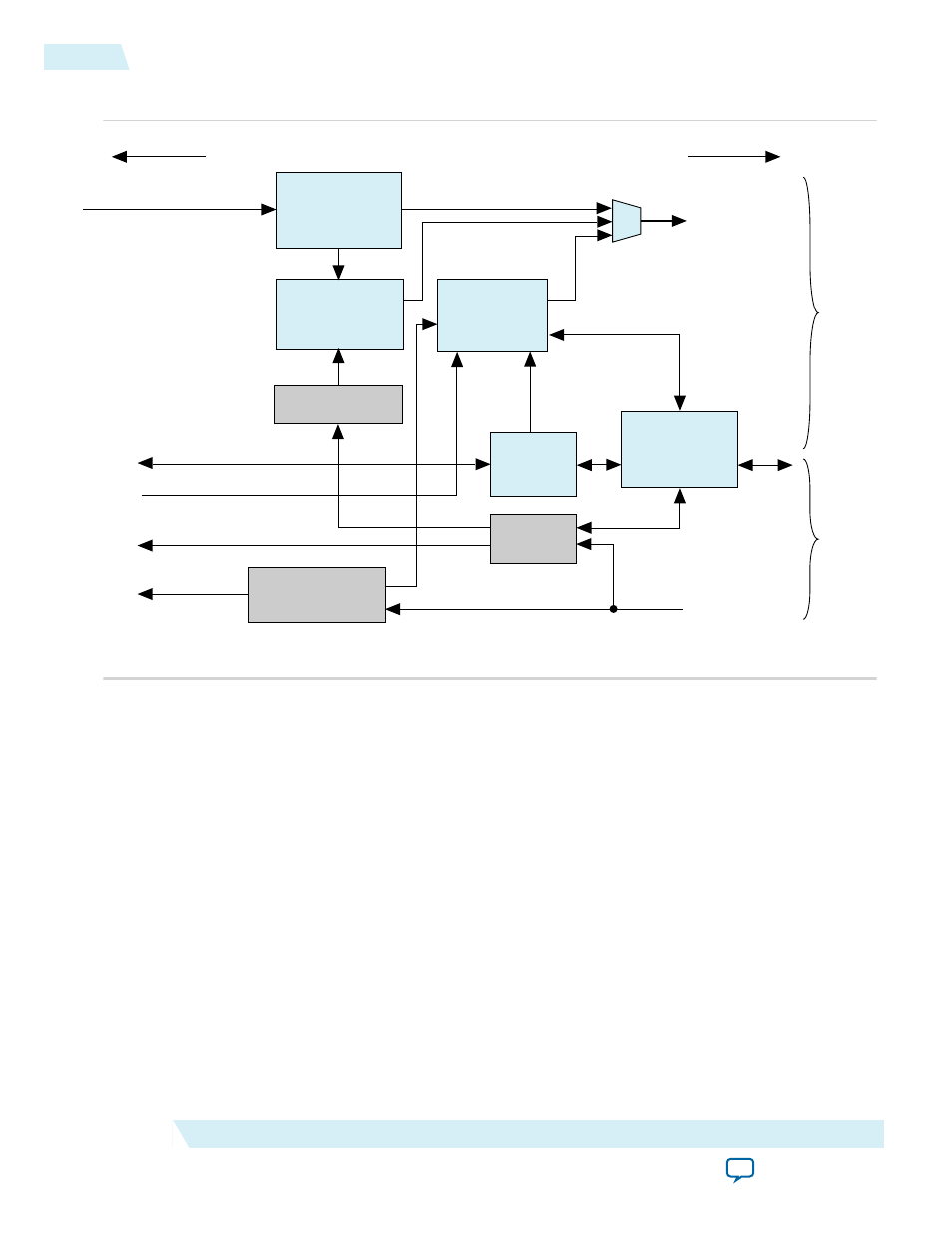

Figure 9-3: Data Link Layer

To Transaction Layer

Tx Transaction Layer

Packet Description & Data

Transaction Layer

Packet Generator

Retry Buffer

To Physical Layer

Tx Packets

Ack/Nack

Packets

RX Datapath

TX Datapath

Rx Packets

DLLP

Checker

Transaction Layer

Packet Checker

DLLP

Generator

Tx Arbitration

Data Link Control

and Management

State Machine

Control

& Status

Configuration Space

Tx Flow Control Credits

Rx Flow Control Credits

Rx Transation Layer

Packet Description & Data

Power

Management

Function

The DLL has the following sub-blocks:

• Data Link Control and Management State Machine—This state machine is synchronized with the

Physical Layer’s LTSSM state machine and is also connected to the Configuration Space Registers. It

initializes the link and flow control credits and reports status to the Configuration Space.

• Power Management—This function handles the handshake to enter low power mode. Such a

transition is based on register values in the Configuration Space and received Power Management

(PM) DLLPs.

• Data Link Layer Packet Generator and Checker—This block is associated with the DLLP’s 16-bit CRC

and maintains the integrity of transmitted packets.

• Transaction Layer Packet Generator—This block generates transmit packets, generating a sequence

number and a 32-bit CRC (LCRC). The packets are also sent to the retry buffer for internal storage. In

retry mode, the TLP generator receives the packets from the retry buffer and generates the CRC for the

transmit packet.

• Retry Buffer—The retry buffer stores TLPs and retransmits all unacknowledged packets in the case of

NAK DLLP reception. In case of ACK DLLP reception, the retry buffer discards all acknowledged

packets.

9-8

Data Link Layer

2014.12.15

Altera Corporation

IP Core Architecture