System bus, Figure214 the system bus, Intel pentium iv processor – HP A7818-IE002 User Manual

Page 58

System Board

System Bus

Chapter 2

58

System Bus

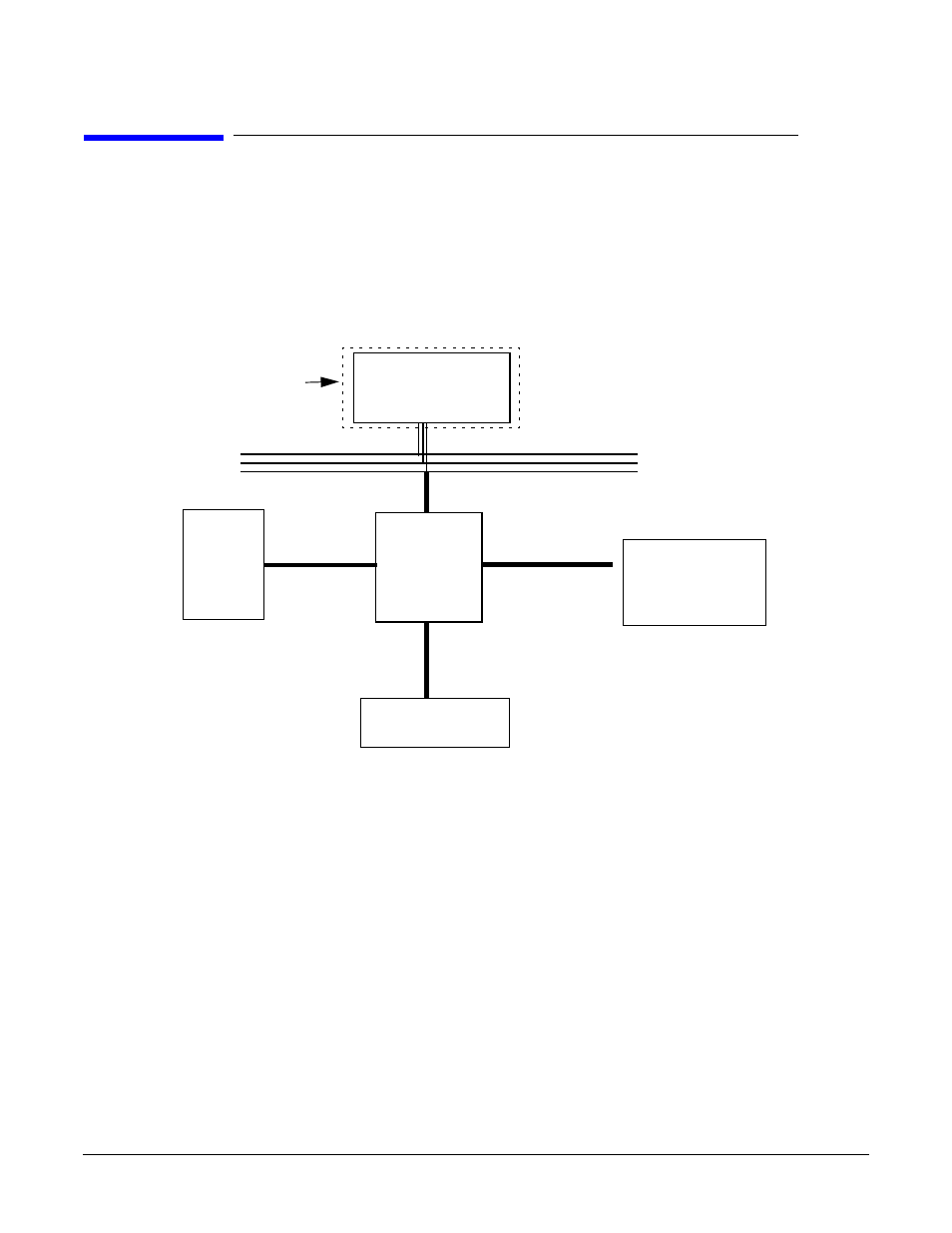

The system bus of the Pentium IV processor is implemented in the Gunning Transceiver

Logic (GTL)+ technology. This technology features open-drain signal drivers that are

pulled up through resistors at bus extremities to the operating voltage of the processor

core. These resistors also act as bus terminators and are integrated in the processor and

in the 82850 MCH.

Figure 2-14

The System Bus

The supported operating frequency of the GTL+ bus for the Pentium IV is 100MHz. The

width of the data bus is 64 bits, whereas the width of the address is 32 bits. Data bus

transfers occur at four times the system bus, at 400MHz. Along with the operating

frequencies, the processor voltage is set automatically.

The control signals of the system bus allow the implementation of a “split -transaction”

bus protocol. This allows the Pentium IV processor to send its request (for example, for

the contents of a given memory address) and release the bus, rather than waiting for the

result. Therefore, processor can accept another request. The MCH, as the target device,

then requests the bus again when it is ready to respond, and sends the requested data

packet. As many as four transactions can be outstanding at any given time.

Intel Pentium IV Processor

The Pentium IV processor has several features that enhance performance:

•

Data bus frequency of 400MHz

850

Memory

Controller Hub

(MCH)

82850

1.5V

AGP

Pro

Connector

I/O Controller Hub

(ICH) 82801AA

Dual Rambus channel

Address (32)

Control

Data (64)

AGP 4x Bus

(133MHz

(1GB/sec data

transfer rate)

Socket 423

100MHz two-way sys-

tem bus (data bus runs at

4 x 100MHz, 3.2GB/s

transfer rate)

HUB LINK 8

(266MB/s

data transfer

rate)

3.2GB/s at

400MHz data

transfer rate)

4 onboard RIMM

sockets

supporting

RDRAM memory

Intel Pentium IV

Processor