Table – HP A7818-IE002 User Manual

Page 39

System Board

Memory Controller Hub (82850)

Chapter 2

39

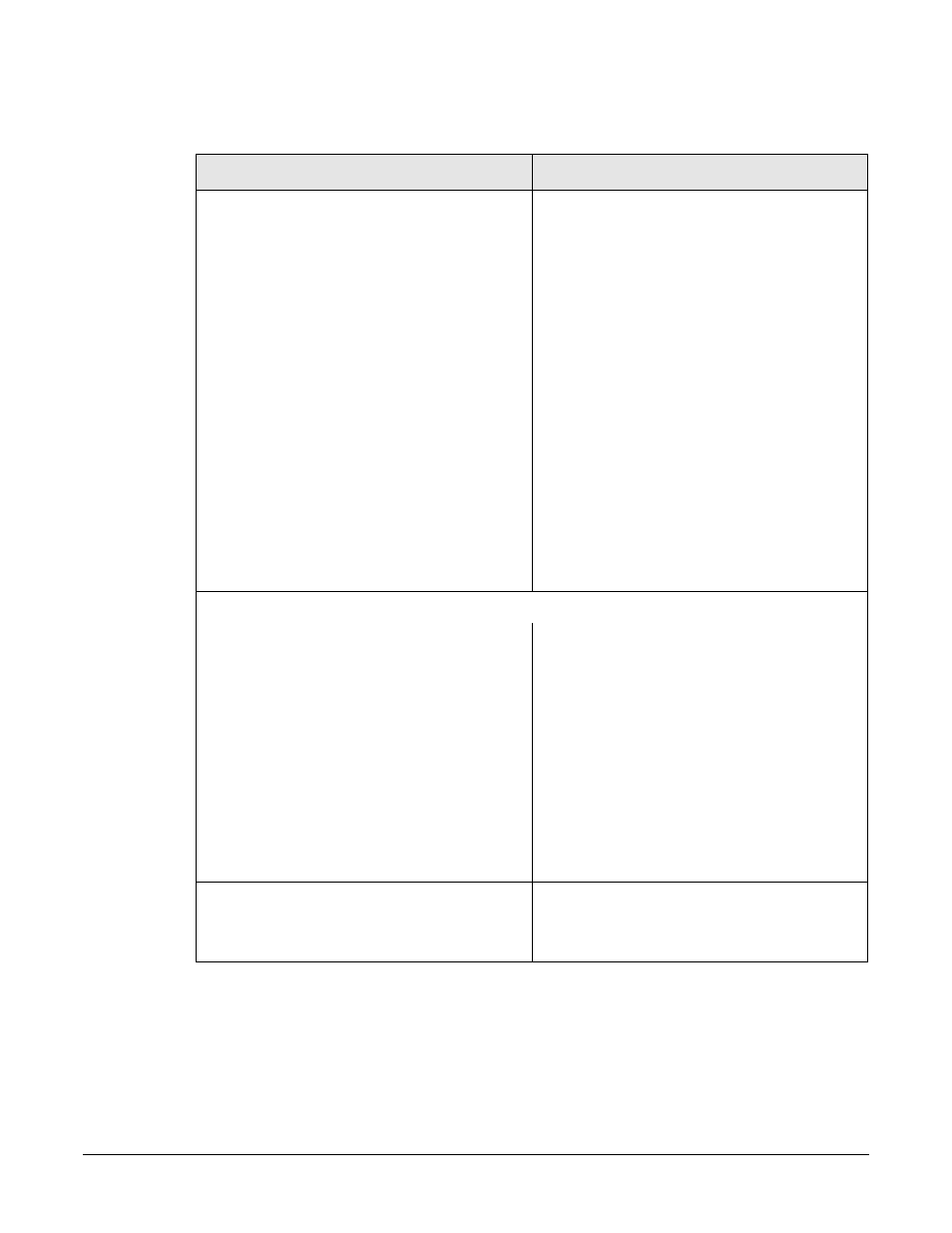

The following table shows the features that the MCH host bridge/controller offers.

Feature

Feature

•

Processor/system bus:

—

Supports Pentium IV processor at

100MHz system bus frequency (400MHz

data bus)

—

Provides an eight-deep In-Order Queue

that supports as many as eight

outstanding transaction requests on the

system bus

—

Desktop optimized AGTL+ bus driver

technology with integrated AGTL +

termination resistors

—

Support for 32-bit system bus address

•

Accelerated Graphics Port (AGP) interface:

—

Single 1.5V AGP Pro connector

—

AGP 2.0 compliant, including AGP 4x

data transfers and 2x/4x Fast Write

protocol

—

AGP 1.5V connector support with 1.5V

signalling only

—

AGP PIPE# or SBA initiated accesses to

DRAM is not snooped

—

AGP FRAME initiated accesses to

DRAM are snooped

(snooper identifies that data is coherent

in cache memory)

—

Hierarchical PCI configuration

mechanism

—

Delayed transaction support for

AGP-to-DRAM reads that cannot be

serviced immediately

•

Memory Controller

Direct Rambus:

•

Dual Direct Rambus Channels operating in

lock-step (both channels must be populated

with a memory module).

Supporting 300MHz or 400MHz

•

RDRAM 128Mbit and 256Mbit devices

•

Minimum upgrade increment of 32MB using

128Mbit DRAM technology

•

As many as 64 Direct Rambus devices

•

Dual-channel maximum memory array size

is:

—

1GB using 128Mbit DRAM technology

—

2GB using 256Mbit DRAM technology

•

As many as eight simultaneous open pages:

—

1KB page size support for 128Mbit and

256Mbit RDRAM devices

—

2KB page size support for 256Mbit

RDRAM devices

•

Hub Link 8-bit interface to ICH2:

—

High-speed interconnect between the

MCH and ICH2 (266MB/sec)