Altera Stratix V Avalon-MM Interface for PCIe Solutions User Manual

Page 63

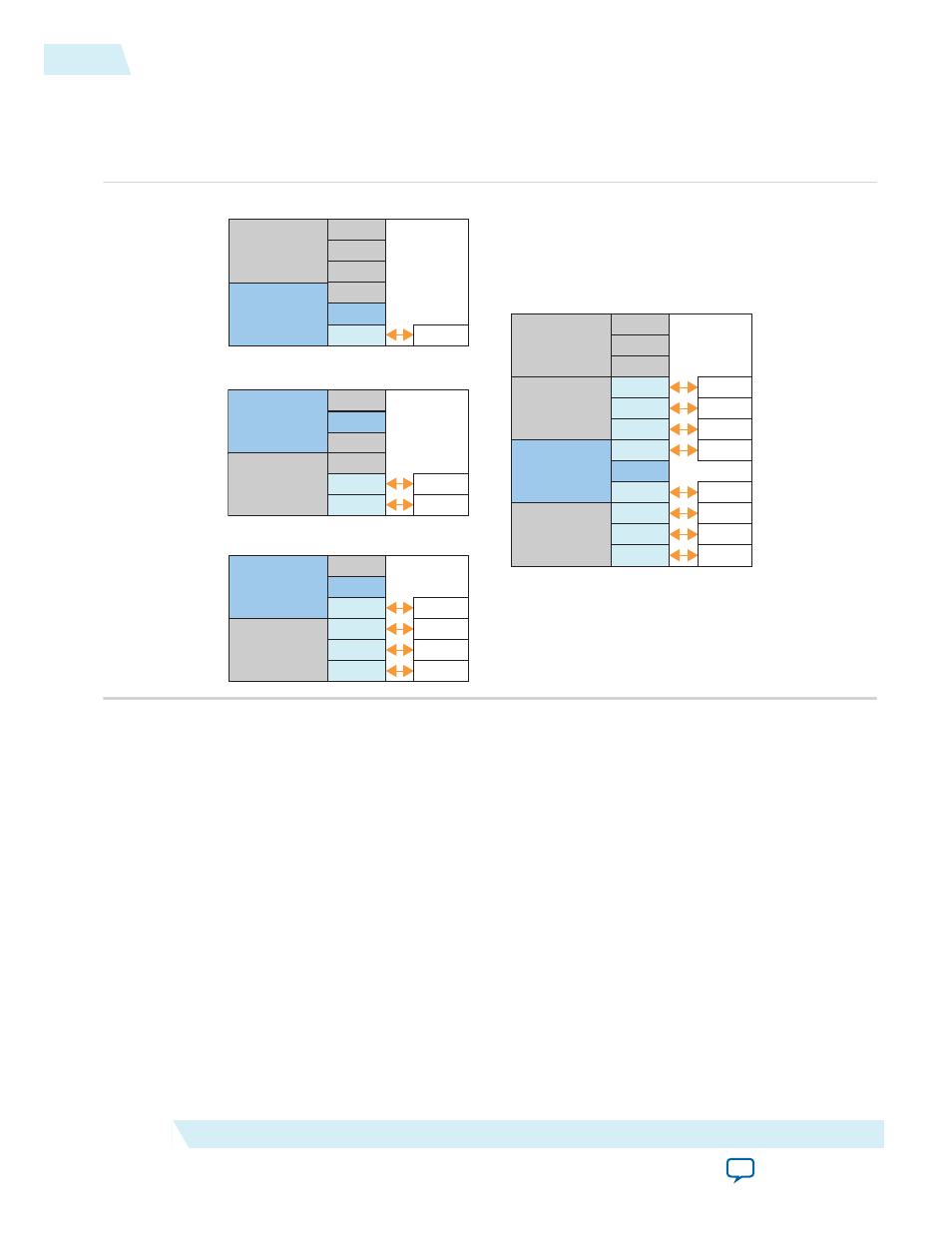

Figure 4-11: Arria V GZ and Stratix V GX/GT/GS Gen3 Channel Placement Using the CMU and ATX PLLs

Gen3 requires two PLLs to facilitate rate switching between the Gen1, Gen2, and Gen3 data rates.

Channels shaded in blue provide the transmit CMU PLL generating the high-speed serial clock. The ATX

PLL shaded in blue is the ATX PLL used in these configurations.

Ch5

Ch3

Ch2

CMU PLL

Ch0

ATX PLL0 Gen3

Ch4

PCIe Hard IP

Ch0

Ch5

Ch3

Ch2

PCIe Hard IP

Ch0

Ch1

Ch0

Ch5

Ch3

Ch2

Ch1

Ch1

Ch0

PCIe Hard IP

Ch0

Ch1

Ch2

Ch3

ATX PLL1 Gen3

ATX PLL0

ATX PLL1 Gen3

ATX PLL0

Ch5

Ch3

Ch2

Ch1

Ch0

Ch0

Ch1

Ch2

Ch3

Ch11

Ch9

Ch8

Ch7

Ch6

Ch10

PCIe Hard IP

Ch5

Ch6

Ch7

Ch4

ATX PLL0

ATX PLL1 Gen3

ATX PLL0

CMU PLL

ATX PLL1

x1

x8

x2

x4

CMU PLL

CMU PLL

ATX PLL1

4-30

Channel Placement in Arria V GZ and Stratix V GX/GT/GS Devices

UG-01097_avmm

2014.12.15

Altera Corporation

64- or 128-Bit Avalon-MM Interface to the Application Layer